- 在复用检测和线性校验码检测的基础上,提出互补存储、奇偶校验和汉明码校验三种存储单元的抗故障攻击防护方案。应用这三种方案,用硬件描述语言Verilog设计了三种抗故障攻击双端口RAM存储器,在Altera 公司的器件EP1C12Q240C8上予以实现。

- 关键字:

汉明码校验 存储单元 Verilog

- 通过对步进电机的驱动控制原理的分析,利用Verilog语言进行层次化设计,最后实现了基于FPGA步进电机的驱动控制系统。该系统可以实现步进电机按既定角度和方向转动及定位控制等功能。仿真和综合的结果表明,该系统不但可以达到对步进电机的驱动控制,同时也优化了传统的系统结构,提高了系统的抗干扰能力和稳定性,可用于工业自动化、办公自动化等应用场合。

- 关键字:

步进电机 Verilog FPGA

- 采用FPGA可编程逻辑器件和硬件描述语言Verilog实现了时钟IP核数据传输、调时和闹铃等功能设计.在此基础上,分析和讨论IP核功能仿真和优化的方法,并通过Modelsim仿真工具和Design Compile逻辑综合优化工具对设计进行仿真、综合和优化,证明了设计的可行性.

- 关键字:

Verilog 时钟IP核 Modelsim仿真

- SPI 总线是一个同步串行接口的数据总线,具有全双工、信号线少、协议简单、传输速度快等特点。介绍了SPI 总线的结构和工作原理,对4 种工作模式的异同进行了比较,并着重分析了SPI 总线的工作时序。利用Verilog 硬件描述语言编写出SPI 总线的主机模块,经ModelSim 仿真得出相应的仿真波形。

- 关键字:

SPI 同步串行接口 Verilog

- 研究基于Avalon-ST接口帧读取的IP核设计应用,通过Avalon-ST接口将外部存储中不同格式的帧数据转化为视频流输出。根据Avalon总线协议及Avalon-ST视频协议研究设计方案,使用Verilog HDL语言对模块进行硬件设计,并将实现的模块进行测试。

- 关键字:

Avalon-ST IP核 Verilog

- 本文选用Xilinx公司的SpananIII系列XC3S200器件,利用硬件描述语言Verilog设计了液晶显示拧制器,实现了替代专用集成电路驱动控制LCD的作用。

- 关键字:

Verilog 液晶显示拧制器 LCD

- 介绍了HDLC协议控制器的IP核方案及实现方法,分别对发送和接收模块进行了分析,给出了仿真波形图。该设计采用Verilog HDL语言进行描述,用ModelSim SE 6.0进行了功能仿真。

- 关键字:

IP核 Verilog HDLC协议控制器

- Verilog HDL是硬件描述语言的一种,用于数字电子系统设计。它允许设计者用它来进行各种级别的逻辑设计,可以用它进行数字逻辑系统的仿真验证、时序分析、逻辑综合。它是目前应用最广泛的一种硬件描述语言之一。Verilog HDL是在1983年由GDA公司的Phil Moorby首创的。

- 关键字:

VerilogHDL VHDL Verilog-XL 华清远见

- 本节通过Verilog HDL语言编写一个具有“百分秒、秒、分”计时功能的数字跑表,可以实现一个小时以内精确至百分之一秒的计时。

- 关键字:

计数器 数字跑表 Verilog

- 本文主要研究了代码加速和代码转换到硬件协处理器的方法。我们还分析了通过一个涉及到基于辅助处理器单元(APU)的实际图像显示案例的基准数据均衡决策的过程。该设计使用了在一个平台FPGA中实现的一个嵌入式PowerPC。

- 关键字:

协处理器 代码加速 HDL

- 文章简要介绍了从光电容积脉搏波中提取出的特征值有助于在医学领域中分析人体的病理特征。为了检测脉搏波的血流参数,整个系统采用Altera公司cyclone系列的FPGA开发平台,运用硬件语言Verilog HDL编程设计了波形参数的检测模块,通过设计IP核进行数据处理并实现了脉搏波的实时检测。使用了QuartusⅡ、Icarus verilog和GTKwave软件进行综合仿真,并通过FPGA原型验证。创新点在于采用FPGA通过硬件的方式提高了实时检测的速度,降低了开发成本,增强了可携带性。

- 关键字:

病理特征 Verilog 原型验证

- 简述了I2C总线的特点;介绍了开发FPGA时I2C总线模块的设计思路;给出并解释了用Verilog HDL实现部分I2C总线功能的程序,以及I2C总线主从模式下的仿真时序图。

- 关键字:

Verilog I2C 仿真时序

- SMBus是一种高效的同步串行总线。通过分析SMBus总线协议,提出了一种运行于基于PCI-Express技术的桥接芯片上的SMBus控制器的设计方案,并且用Verilog语言描述,最后在Altera公司的FPGA上得以实现。通过仿真测试,证明该方法是稳定有效的。

- 关键字:

SMBus总线 Verilog 有限状态机

- LCD显示屏的应用越来越广,数量越来越多。LCD显示屏应用广泛,无处不在。如家庭各种电器设备。更常见是用于各种公共场合如体育馆、广场等商业用途。给我们传递一种更为直观、生动的信息。从此我们的生活发生了巨大改变。巨大的应用巨大的市场带来了巨大的商机。基于FPGA的LCD显示的3D影像是为了LCD显示屏的信息量更多,满足人需求。

- 关键字:

IP核 3D图像处理器 FPGA LCD Verilog

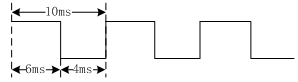

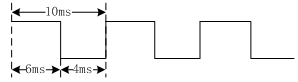

- 一、 功能描述 脉冲宽度调制(pulse width modelation)简称PWM,利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术,广泛应用在从测量、通信到功率控制与变换的许多领域中脉冲宽度调制是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术,广泛应用在从测量、通信到功率控制与变换的许多领域中。 在本章的应用中可以认为PWM就是一种方波。如图所示:

PWM波形图 上图是一个周期为10ms,高电平为

- 关键字:

PWM verilog

.verilog.hdl.介绍

您好,目前还没有人创建词条.verilog.hdl.!

欢迎您创建该词条,阐述对.verilog.hdl.的理解,并与今后在此搜索.verilog.hdl.的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473