现场可编程门阵列(fpga) 文章 进入现场可编程门阵列(fpga)技术社区

用现场可编程门阵列实现的频率计

- 1 引言 数字频率计是通信设备、音、视频等科研生产领域不可缺少的测量仪器。采用Verilog HDL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分外,其余全部在一片FPGA芯片上实现。整个系统非常精简,且具有灵活的现场可更改性。 相比传统的电路系统设计方法,EDA技术采用VHDL语言描述电路系统,包括电路的结构、行为方式、逻辑功能及接口。Verilog HDL具有多层次描述系统硬件功能的能力,支持自顶向下的设计特点。设计者可不必了解硬件结构。从系统设计入手,在顶层

- 关键字: 嵌入式系统 单片机 现场可编程门阵列 频率计 MCU和嵌入式微处理器

FPGA在语音存储与回放系统中的应用

- 1 引言 随着数字信号处理器、超大规模集成电路的高速发展,语音记录技术已从模拟录音阶段过渡到数字录音阶段。在数字化录音技术中,压缩后的语音数据有些存储在硬盘中,有些存储在带有掉电保护功能的RAM或FLASH存储器中。笔者介绍的语音存储与回放系统,未使用专用的语音处理芯片,不需要扩展接口电路,只利用FPGA作为核心控制器,就能完成语音信号的数字化处理,即实现语音的存储与回放。 2 系统总体结构 数字化语音存储与回放系统的基本工作原理是将模拟语音信号通过模数转换器(A/D)转换成数字信号

- 关键字: 嵌入式系统 单片机 FPGA 语音存储 MCU和嵌入式微处理器

采用AVR单片机对FPGA进行配置

- Altera公司的ACEX、FLEX等系列的FPGA芯片应用广泛,但其FPGA基于SRAM结构,决定电路逻辑功能的编程数据存储于SRAM中。由于SRAM的易失性,每次上电时必须重新把编程数据装载到SRAM中,这一过程就是FPGA的配置过程。FPGA的配置分为主动式和被动式。在主动模式下,FPGA上电后主动将配置数据从专用的EPROM(如EPC1,EPC2等)加载到SRAM中。被动模式下,FPGA为从属器件,由相应的控制电路或微处理器控制配置过程,包括通过下载

- 关键字: 单片机 FPGA MCU和嵌入式微处理器

FPGA的堆叠封装,欲革背板与SoC的命

- FPGA最基本的应用是桥接。随着FPGA的门数不断提高,雄心勃勃的FPGA巨头们早已不满足这些,他们向着信号处理、互联性和高速运算方向发展。未来,FPGA还有望与模拟和存储器厂商合作,做出SIP(堆叠封装)。 最近,笔者访问了Xilinx公司的CTO Ivo Bolsens,他说未来的FPGA一方面是在功耗、性能、价格方面进行不停地改进,未来将出现革命性的变化就是利用推迭封装(SIP),一个封装里面放多个裸片的技术,那么FPGA平台可能就会成为一个标准的、虚拟的SoC(Virtual SoC)的

- 关键字: FPGA SoC MCU和嵌入式微处理器

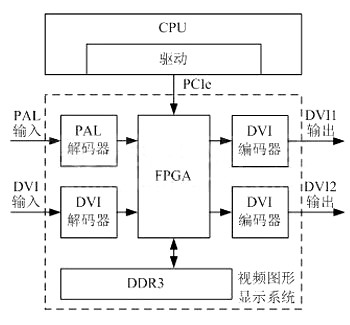

基于FPGA的计算机防视频信息泄漏系统设计

- 假如显示终端为数字微镜DMD(Digital MicromirrorDevice)显示器。该显示器将计算机每个像素点的图像信号经过数字光处理DLP(Digital Light Processing)后,存入SDRAM双向缓存器,当一帧图像接收完毕时,内部数据处理电路同时激发各像素点对应的微镜运动,完成一帧图像的显示。DMD显示器峰值数字驱动电压不超过33.5V,电磁辐射很低,且各微镜片同时驱动,形成相互干扰的向外辐射信号,解码难度极大,从而使其成为无信息泄漏的显示器。此时,视频电缆的辐射在整个视频通路

- 关键字: 嵌入式系统 单片机 FPGA 视频信息 MCU和嵌入式微处理器

嵌入式系统中从串配置FPGA的实现

- 本文主要论述在ARM嵌入式系统中如何实现FPGA从串配置的方法,将系统程序及配置数据存储在系统Flash中,利用ARM的通用I/O口产生配置时序,省去专用的配置PROM。 文中ARM微处理器采用samsung公司的ARM7TDMI系列中的S3C4480X,FPGA采用xilinx 公司spartan3E系列中的XC3S100E,详细讨论FPGA的从串配置的时序,同时论述S3C4480X从串配置spartan3E系列FPGA的软、硬件实现方法。实践证明,该方法在成本、体积、灵活性上均具有优势

- 关键字: 嵌入式系统 单片机 嵌入式 FPGA MCU和嵌入式微处理器

在嵌入式系统中用FPGA进行开发的几个发展方向

- 顾名思义,嵌入式系统指的是嵌入到系统内部的计算机系统,是面向特定应用设计的专用计算机系统。 早期的嵌入式系统一般是以通用处理器或单片机为核心,在外围电路中加入存储器、功率驱动器、通信接口、显示接口、人机输入接口等外围接口,再加上应用软件,有些还加上了嵌入式操作系统,从而构成完整的系统。 随着微电子技术的进步,SoC已经在很多应用中取代了传统的以单片机为中心的架构,将很多外设和存储器集成在一个芯片中,使系统的

- 关键字: 嵌入式系统 FPGA MCU和嵌入式微处理器

现场可编程门阵列(fpga)介绍

您好,目前还没有人创建词条现场可编程门阵列(fpga)!

欢迎您创建该词条,阐述对现场可编程门阵列(fpga)的理解,并与今后在此搜索现场可编程门阵列(fpga)的朋友们分享。 创建词条

欢迎您创建该词条,阐述对现场可编程门阵列(fpga)的理解,并与今后在此搜索现场可编程门阵列(fpga)的朋友们分享。 创建词条