DM368 视频前端信号采集详解

2.2 DM368 视频前端对输入信号的解析

本文引用地址:https://www.eepw.com.cn/article/277978.htm2.2.1 ISIF 对信号的解析

无论是master 模式还是slave 模式,DM368 的视频前端接口ISIF 对于信号的处理是一样的。

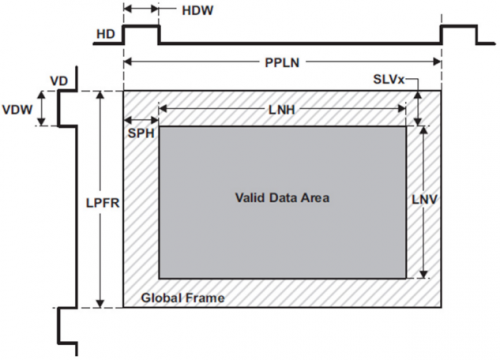

图 2. 帧图像格式

图2 的时序通常认为水平同步和垂直同步信号都为高电平有效,需要配置ISIF 的MODESET. HDPOL=MODESET.VDPOL=0。在这种情况下,水平同步信号宽度为HDW (HD pulse width),以像素为单位。垂直同步信号宽度为 VDW (VD pulse width) ,以行数为单位。 PLLN(Pixels per line)是每行的像素个数,也就是相邻两个行同步信号间的像素个数。LPFR 是Lines per frame 的缩写,表示每帧数据有多少行,也是相邻两个场同步信号之间的行数。在slave 模式下,PLCK/HD/VD 都是外部输入的,ISIF 寄存器HDW/VDW/PLLN 是不需要配置的。图2 中的灰色区域我们叫做有效数据区域,也就是用户希望获得的有效数据。而斜线阴影区域就是消隐区域。消隐区域在视频前端处理中也是必不可少的部分,关于这点我们会在第3 节详细介绍。

如果你使用的是单次(one shot)模式,或者在连续(continuous)模式下,你需要保存RAW 数据,那你就需要配置 SPH( Start pixel horizontal 水平方向起始像素),SLV0/1 (Start line vertical - field 0/1 垂直方向奇偶场起始行),LNH( Number of pixels in line 每行像素个数),LNV (Number of lines vertical 垂直方向行数)。这是为了告诉DM368 你需要把输入的图像的哪部分写到DDR。也就是说你可以选择只输出有效数据里面的某一部分到DDR。

SPH 告诉硬件在同步信号有效以后从哪个像素开始写入DDR。请注意这里的HD 信号有效起始点是指同步信号有效的沿,不是从同步信号脉冲结束后作为计数像素的起点。例如,如果HD 信号高电平有效,就是HD 上升沿后开始计数,LNH 个PCLK(也就是像素)后将接收到的数据写入DDR。同样 SLV0/1 告诉硬件从哪行数据开始需要写入 DDR,LNV 决定了写多少行数据到 DDR。所以调整ISIF 的SPH,SLV0/1, LNH 和LNV 就可以调整保存到DDR 上的RAW 数据在原图中的位置,以及 RAW 数据段大小(长宽)。如果不需要写入 RAW 到DDR,那就不需要配置 SPH, SLV0/1 ,LNH 和LNV。

图2 的时序如果配置为同步信号低电平有效也是可以的。但是如果配置为低电平有效,相关的参数就发生了变化。例如水平同步信号宽度就变为 PPLN-HDW,垂直同步信号宽度为 LPFR- VDW。SPH 和 SLV0/1 都变成了 0。所以在配置 ISIF 相关寄存器前首先需要把同步信号的极性确定下来。 要采集到正确的数据,DM368 采样数据时机必须和传感器输出数据的时机匹配。在DM368 上默认是PCLK 的下降沿采样数据。用户可以通过修改SYSTEM module 寄存器VPSS_CLK_CTRL的PCLK_INV[2] 位来改变 PCLK 采样沿。

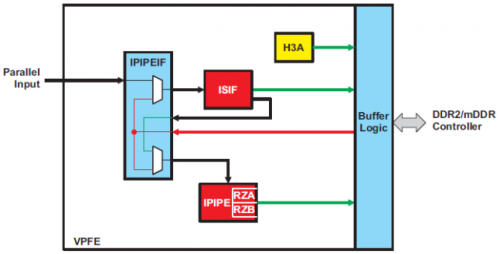

2.2.2 IPIPE 和Resizer 对信号的解析和处理

如果ISIF 直接通过IPIPEIF 连接到IPIPE,那所有的图像数据,也就是图2 里的global frame 都会传输到IPIPE。在IPIPE 里面 用户需要配置SRC_HPS (Horizontal Start Position ),SRC_VPS(Vertical Start Position),SRC_HSZ( Horizontal Processing Size)和SRC_VSZ( Vertical Processing Size),来确认global frame 里面的哪一部分需要IPIPE 来处理。

在resizer 的模块里面,也有SRC_HPS,SRC_VPS,SRC_HSZ 和SRC_VSZ 可以配置resizer处理的图像的区域。如果IPIPE 的输出到resizer 已经是需要处理的区域,那SRC_HPS,SRC_VPS 就可以配置为0,而resizer 的SRC_HSZ,SRC_VSZ 等于IPIPE 的SRC_HSZ,SRC_VSZ。如果ISIF 的输出是通过IPIPEIF 直接到resizer(没有经过IPIPE),resizer 的SRC_HPS,SRC_VPS 就不能配置为0 了,需要用户根据需要处理的图像合理的配置resizer 的SRC_HPS,SRC_VPS 寄存器。

2.2.3 RAW 数据和YUV 数据的匹配

在连续模式下,用户同时获得resizer 输出的YUV 和ISIF 输出的RAW,时常有用户发现自己保存的RAW 数据和Resizer 输出的YUV 数据不匹配,有一定的偏移。这种问题的原因是IPIPE,Resizer 里面的SRC_HPS,SRC_VPS,SRC_HSZ 和SRC_VSZ 和ISIF 里面的写入DDR 时候配置的偏移和大小不匹配。IPIPE/Resizer 和ISIF 的寄存器本身是没有直接关系的,这就需要用户将它们一一对应,匹配起来。例如ISIF 输出的数据输入给IPIPE,为了让RAW 和YUV 匹配,需要ISIF 的SPH 等于IPIPE 的SRC_HPS,ISIF 的SLV0/1 等于IPIPE 的SRC_VPS,ISIF 的LNH 等于IPIPE 的SRC_ HSZ,ISIF 的LNV 等于IPIPE 的SRC_ VSZ。而Resizer 的SRC_HPS,SRC_VPS 需要配置为0,而resizer 的SRC_HSZ,SRC_VSZ 要等于IPIPE 的SRC_HSZ,SRC_VSZ。

在单次模式下,也就是数据通路ISIF->DDR->IPIPEIF->IPIPE(Resizer),由于IPIPE 的输入是DDR 上的RAW 数据,有效数据的获取已经在ISIF 输出到DDR 配置里面实现了,IPIPE 里面的处理数据的起始位置就可以是(0,0)了。

这样无论是在连续模式还是在单次模式下,RAW 数据和RAW 输出转换出的YUV 数据就可以完全匹配了。

评论