基于XCR3256的低功耗存储测试器研究设计

2 低功耗的实现方法

降低系统功耗的传统手段主要集中在硬件上, 如:选择低功耗器件、安排不同的供电回路等。然而,硬件只是一个平台,软件的作用不容忽视,总线上几乎每一个芯片的访问、每一个信号的翻转差不多都由软件控制,如果软件能减少外存的访问次数、及时响应中断等都将对降低功耗作出很大的贡献。

2.1 硬件

2.1.1 芯片级低功耗实现技术

在该设计中大部分器件如主控芯片、存储器、总线驱动器、FIFO等都是采用的CMOS、HMOS低功耗器件。

主控芯片选用的Xilinx公司的CPLD,型号为XCR3256,3.3V工作电压,低功耗运作,5V与3.3V兼容I/O端口。对于不用的 I/O口全部设为输出(外面不接任何有驱动的信号)。如果I/O悬空的话,受外界的一点点干扰就可能成为反复振荡的输入信号了,而CMOS器件的功耗基本取决于门电路的翻转次数。此外,悬空的输入引脚由于处于0, 1 之间的过渡区, 可使电路中的反相器P 沟道和N 沟道都处于导通状态, 也将导致CPLD本身功耗增大。如果把它们上拉,每个引脚也会有微安级的电流。因此,在设计中将不同的I/O全部设为输出。

2.1.2 电路级低功耗实现技术

公式(1)为CMOS电路功耗的计算公式[3]。式中:P为静态和动态功耗总合;m为节点数;n为器件总数;VDD为工作电压;fak为时钟频率;ILn为反向漏电流;ISCn为瞬态短路电流;am为节点充电率;cm为节点电容。

从该公式中可见降低系统工作电压可达到降低系统功耗的目的。对于中心控制模块采用专用的低电压电源模块TPS70358进行供电。TPS70358可以提供3.3V/2.5V两组供电方式,同时它本身还具有电源管理功能。

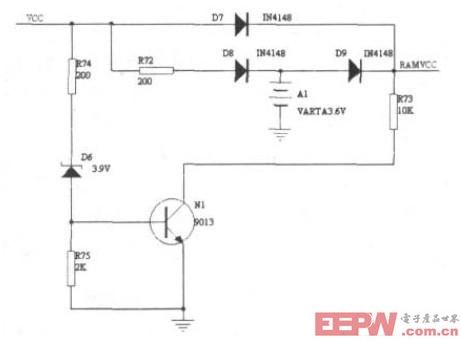

图4为低功耗数据保持电路,在存在系统供电时,可对电池进行充电,当系统掉电时可由电池对存储器进行供电,实现数据的自保持。存储器的静态功耗仅为10mW ,由计算可知该电路实现的数据保持期可达一年以上。

图4 低功耗数据保持电路

评论