选择合适的示波器进行高速电路调试和验证

示波器,作为全球使用最广的通用仪器,伴随电子设计工程师走过了60年的历程。第一代的模拟实时示波器(ART)和第二代的数字存储示波器(DSO),都有其明显的缺点。基于DPX数字荧光技术的第三代数字荧光示波器(DPO),结合了前两代示波器的优点,同时消除了两者的缺点。全新一代的数字荧光技术进一步提升了数字荧光示波器的实时性,使DPO在性能和适用性方面已经远远超过了同等带宽的ART和DSO,成为当前业界性能最优、效率最高、分析能力最强的选择。为什么DPO具有这样的能力呢?本文接下来的部分,将结合DPX技术的核心,为读者完整介绍三代示波器在调试和验证工作中的优劣势,同时解答一些已谈论过多年的疑问。

第一章 示波器技术的发展和演变

泰克的 511模拟实时示波器,标志着商用示波器时代的到来。511之前也有一些“示波器”产品,但是由于其没有触发系统和校准的时基、垂直刻度,不能提供稳定的显示波形,也不能进行定量测试,所以只是一种定性观测的工具。511首次在“示波器”这种测试设备中加入了边沿触发以显示稳定波形、使用校准的时基和垂直放大器以提供定量测试能力,大大增加了适用性。这样,商用示波器诞生了。

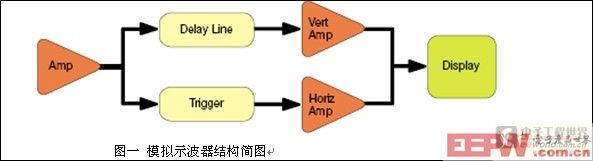

模拟实时示波器发展到现在,基本结构并没有多大变化,下图是一个基本的结构框图:

图1: 模拟示波器结构简图

模拟实时示波器机构简单,没有信号的数字化、处理等过程。ART的所有信号调理、放大和显示都由模拟器件完成,所以从信号进入放大器(或探头)到最后在CRT上显示,几乎是实时(延迟时间几乎可以忽略)的。

但 是,模拟示波器也有死区时间,在死区时间内出现的信号是不能显示在屏幕上的。这个死区时间来自于触发系统的“触发抑止(hold off)”和等待触发的时间。所以,模拟示波器也不是能100%地捕获信号。不同型号的模拟实时示波器,最大波形捕获概率大约从30%~70%不等,扫描速度最快可达50万次/秒。这是一个非常好的指标。

再来看模拟示波器显示的方式——CRT阴极射线管。电子束经过偏转板的偏转,再轰击显示屏上的荧光物质发光形成波形轨迹。当电子束停止轰击后,亮点不会立即消失而要保留一段余辉时间。余辉时间10μs—1ms为短余辉,1ms—0.1s 为中余辉,0.1s-1s为长余辉,大于1s为极长余辉。一般的示波器配备中余辉示波管,高频示波器选用短余辉,低频示波器选用长余辉。在余辉效应的作用下,波形轨迹上每一点的亮度,和被轰击的次数(频度)成正比关系。因此,模拟实时示波器显示的波形,不仅有时间和幅度的信息,还能以亮度等级表示信号出现概率的信息,非常有利于观测。

但是在另一方面,荧光物质发光的这一特性也带来了一个问题:轰击次数过少的轨迹的亮度会很低,甚至根本无法观测到。所以模拟示波器比较适合于重复信号(如连续正弦波)或者有重复特性的信号(如模拟视频信号)。而对单次信号(如单个脉冲或偶发故障)的观测能力非常有限。

总结起来,模拟实时示波器有以下几点主要优点:实时性强、波形捕获概率高、直观的三维(时间、幅度和信号出现概率)显示方式。缺点主要在于:无法存储数据、分析能力有限、对低概率事件捕获能力不足、触发简单、预触发延时不足和带宽提升困难(从前端放大器到CRT必须同时提升)等。随着数字化运动的兴起和越来越多的单次信号测量需求,模拟示波器这些缺点使其渐渐不再能满足测试需求,所以从上世纪80年代开始,主流的示波器厂家均渐渐转向数字示波器的研发和生产。

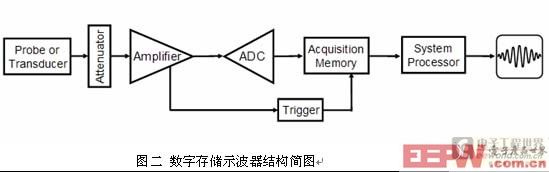

第一代数字示波器现在被称为数字存储示波器(DSO),使用串行的工作结构。原理框图如下:

图2: 数字存储示波器结构简图

数字存储示波器使用了ADC采样的方式,所以被测的模拟波形最终可以以数据的格式存储。当然,数字化的数据还可以方便地进行自动测量、频谱分析、数学计算或者其它高级分析。所以数字示波器特别适于单次信号的采集和分析,这是一个很大的突破。

另外一方面,数字存储示波器在ADC以后就是全数字化处理,所以带宽的提升仅受限于可变增益的前置放大器带宽和ADC的速率。随着技术的进步,现在,泰克 TDS6154C是业界真实模拟代宽最高的数字存储示波器,达到12.5GHz(3dB)。由于超高高带宽示波器系统设计中,宽带放大器是其中的核心部分,目前的主流设计都采用每一个通道独立的硬件放大器设计方法,这样保证每一个通道的性能没有限制。当每一个通道放大器的设计带宽不足时,有些示波器通过DBI技术利用示波器每一个通道6GHZ的低带宽放大器在不同的频段“拼接”在一起,在某一个通道上达到超过6GHZ的带宽,例如3个通道的6GHZ频段“拼接”后达到18GHZ带宽。从DBI技术实现的方法可以明显看出它的优点和相应的缺陷,最明显的优势是利用多通道的低带宽合并为单通道超过10GHZ的高带宽,在示波器设计中成本最高的放大器和ADC均采用低速设计,非常有利于控制成本。由于DBI技术本质上首先经过将信号频率分配到不同的通道,通过相对低速的ADC进行采样,最后通过DSP技术将这些包含不同分量的频率数字“拼接”,它会导致以下几个限制。

评论