一种新型带GPRS接口的数码防伪读码器的设计

1 存储器设计

微处理器S3C44BOX的存储控制器可以为片外存储器访问提供必要的控制信号。每个地址空间的数据总线宽度是可以通过编程或引脚连接来配置的,由于系统上电启动或复位后总是从0X00000000地址开始执行,Boo映射后的地址就是0X00000000,所以必须在第一次访问ROM前设置Bank0的数据总线宽度。系统中将OM0通过上拉电阻与VDD相连接,OM1通过下拉电阻与GND相连接,即Bank0选用的是16位的数据总线宽度。

除了Bank0以外的其他地址空间可以在系统的启动代码中通过编程予以设置,具体是通过设置存储器控制专用寄存器BWSCON来实现的。存储器控制专用寄存器包括总线宽度/等待控制寄存器、Bank控制寄存器、刷新控制寄存器、Bank大小控制寄存器和模式寄存器设置寄存器,各个寄存器的每一数据位的具体含义请参考数据手册。

根据所选择的Flash和SDRAM,系统各地址空间的数据总线宽度都设置为16位,存储模式为小端模式,不使用等待状态,不使用UB/LB。

2 串口设计

ARM S3C44BOX的UART单元带两个异步串行口,皆可工作于中断和DMA模式,各带有16字节的FIFO。最大波特率115.2K。DART单元包括可编程波特率、红外发送/接收、1个或2个停止位、5/6/7/8位数据宽度和奇偶校验位。每个DART有7种状态:溢出错误、校验错误、帧错误、暂停态、接收缓冲区准备好、发送缓冲区空、发送移位缓冲器空等,这些状态可以由相应的UTRSTATn/UERSTATn表示,并且与发送接收缓冲区相对应的有错误缓冲区。波特率可以通过控制波特率寄存器进行设置。每一个DART的波特率发生器为收/发器提供一个连续时钟,时钟源可选为S3C44BOX的内部系统时钟。波特率的时钟通过一个16位分频器分频后产生,16位分频器的值由寄存器UBRDIVn寄存器具体说明。

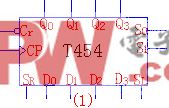

根据系统功能的需要,读码器在调试过程中需要与PC进行通信,所以需要在微处理器和PC之间设计电平转换电路。另外,系统与存放产品功号的芯片需要进行通信,这里不需要电平转换,系统在GPRS接口中直接将串口线引出,其中的部分引脚即可作为与存储芯片连接的接口,连接电路如图2所示。

评论