串行接口LED数码管及键盘管理ZLG7289A的原理与应用

3.2 带有数据的指令

(1)下载数据且按方式0译码指令

该指令的格式如下:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 0 | 0 | 0 | 0 | a2 | a1 | a0 |

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| DP | X | X | X | d3 | d2 | d0 | d1 |

该命令由二个字节组成。前半部分为指令,其中a2 a1 a0 为位地址,d0~d3为数据。具体分配方式如表2所列。当系统接收到此指令时(ZLG7289A将按译码方式0进行译码)具体的译码方式如表3所列。小数点的显示可由DP位控制,DP为1时,小数点显示,DP为0时,小数点不显示。在该指令格式中,x表示没有影响。

表2 位地址分配表

| a2 | a1 | a0 | 显示位 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 2 |

| 0 | 1 | 0 | 3 |

| 0 | 1 | 1 | 4 |

| 1 | 0 | 0 | 5 |

| 1 | 0 | 1 | 6 |

| 1 | 1 | 0 | 7 |

| 1 | 1 | 1 | 8 |

表3 译码方式表

| d0~d3 | d3 | d2 | d1 | d0 | 7段显示 |

| 00H | 0 | 0 | 0 | 0 | 0 |

| 01H | 0 | 0 | 1 | 1 | 1 |

| 02H | 0 | 0 | 0 | 0 | 2 |

| 03H | 0 | 0 | 1 | 1 | 3 |

| 04H | 0 | 1 | 0 | 0 | 4 |

| 05H | 0 | 1 | 0 | 1 | 5 |

| 06H | 0 | 1 | 1 | 0 | 6 |

| 07H | 0 | 1 | 1 | 1 | 7 |

| 08H | 1 | 0 | 0 | 0 | 8 |

| 09H | 1 | 0 | 0 | 1 | 9 |

| 0AH | 1 | 0 | 1 | 0 | - |

| 0BH | 1 | 0 | 1 | 1 | E |

| 0CH | 1 | 1 | 0 | 0 | H |

| 0DH | 1 | 1 | 0 | 1 | L |

| 0EH | 1 | 1 | 1 | 0 | P |

| 0FH | 1 | 1 | 1 | 1 | 空无显示 |

(2)下载数据且按方式1译码指令

这种指令与上一个指令基本相同。所不同的是,该指令的d0~d3对应的数据位0AH~0FH分别为七段显示中的A、B、C、D、E、F。该指令的具体格式如下:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 1 | 0 | 0 | 1 | a2 | a1 | a0 |

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| DP | X | X | X | d3 | d2 | d0 | d1 |

(3) 读键盘数据指令

该指令从ZLG7289A读出当前的按键代码,格式如下:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| d7 | d6 | d5 | d4 | d3 | d2 | d0 | d1 |

与其它指令不同的是,此命令的前一个字节0001010B 为单片机传送到ZLG7289A的指令,而后一个字节d0~d7则为ZLG7289A返回的按键代码。 其范围为0~3FH(无键按下时为0xFF)。在此指令的前半段,ZLG7289A 的DATA 引脚处于高阻输入状态,可以用来接收来自微处理器的指令;在指令的后半段,DATA 引脚从输入状态转为输出状态,此时将输出键盘代码的值。故微处理器连接到DATA 引脚的I/O口应当有一个从输出态到输入态的转换过程。

当ZLG7289A检测到有效的按键时,KEY 脚将从高电平变为低电平,并一直保持到按键结束。在此期间,如果ZLG7289A 接收到“读键盘数据指令”,则输出当前按键的键盘代码;如果在接收到“读键盘数据指令”时没有有效按键,ZLG7289A将输出FFH(11111111B)。

(4)其它指令

除以上几个指令外,ZLG7289A还具有下载数据但不译码、闪烁控制、消隐控制、段点亮指令、段关闭等指令,限于篇幅,此处不再详述。

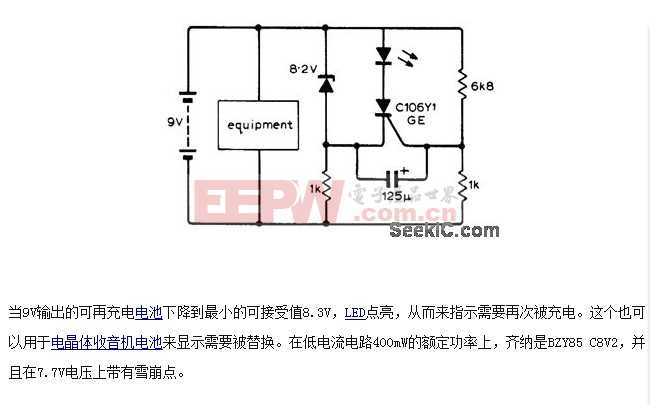

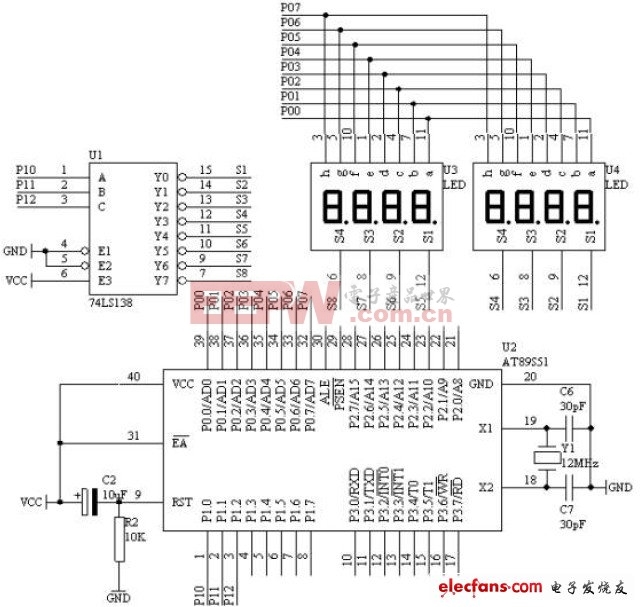

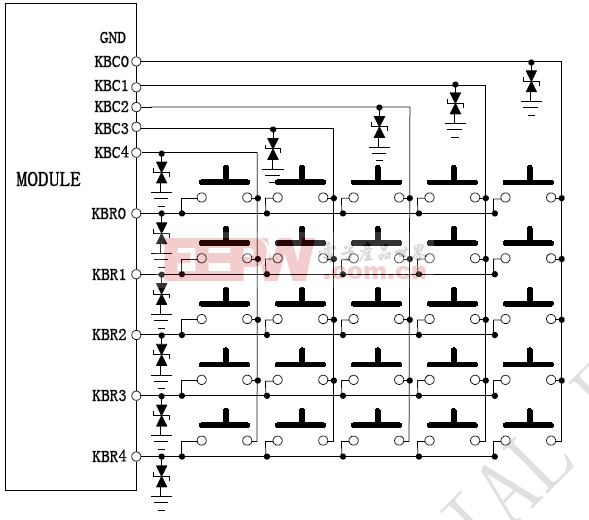

图2

4 典型应用

ZLG7289A 的典型应用电路如图2所示,图中,ZLG7289A 应连接共阴式数码管,应用中无需用到的数码管和键盘可以不连接,因而可省去数码管。此外,设置消隐属性也不会影响键盘的使用。

由于ZLG7289采用的是循环扫描的工作方式,因此,如果采用普通的数码管,亮度可能不够,故应采用高亮度或超高亮度的数码管,且尺寸也不宜选的过大,一般字符高度不超过1 英寸,如使用大型的数码管,则应选用适当的驱动电路。

ZLG7289A的RESET复位端在一般情况下,可以直接和VCC相连;而在需要较高可靠性的情况下,则可以连接外部复位电路或直接由MCU 控制。在上电或RESET 端由低电平变为高电平后,通常要经过大约18~25ms的时间,ZLG7289A才会进入正常工作状态。

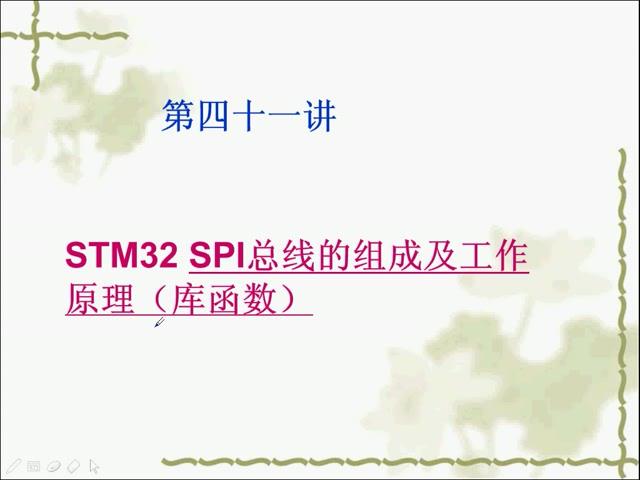

图3

5 应用实例

图3是以AT89C51单片机为例给出的ZLG7289A与单片机的接口电路。图中,AT89C51所用时钟频率为12MHz如果使用不同的CPU时钟频率,则应注意调整延时时间。下面给出的是该系统的部分程序:

;*****************RAM定义

BIT_COUNT DATA 07FH

TIMER DATA 07EH

TIMER1 DATA 07DH

TEN DATA 07CH

DATA_IN DATA 020H

DATA_OUT DATA 021H

;**************I/O定义

DAT BIT P0.6 ;ZLG8279A的 DATA,连接AT89C51的P0.6

KEY BIT P0.7 ; ZLG8279A的KEY,连接AT89C51的P0.7

CS BIT P0.4 ; ZLG8279A的CS,连接AT89C51的P0.4

CLK BIT P0.5 ; ZLG8279A的CLK,连接AT89C51的P0.5

ORG 0000H

AJMP START

ORG 0030H

START:MOV SP,#2FH ;堆栈定义

MOV P1,#11011011B ;I/O初始化

MOV TIMER,#50 ;25ms定时

START_DELAY: MOV TIMER1,#255

START_DELAY1: DJNZ TIMER1,START_DELAY1

DJNZ TIMER,START_DELAY

MOV DATA_OUT,#10100100B ;复位指令

CALL SEND ;发指令到ZLG8279A

SETB CS ;恢复CS高电平

MAIN:JB KEY,MAIN ;是否有键按下

MOV DATA_OUT,#00010101B ;有键按下,发读键盘指令

CALL SEND

CALL RECEIVE

SETB CS ;CS置高电平

MOV B,#10 ;16进制到BCD码转换

MOV A,DATA_IN

DIV AB

MOV TEN,A

MOV DATA_OUT,#10100001B ;左移指令

CALL SEND

评论