基于PCI软“核”的PCI总线接口设计与实现

STOP_USR 是STOP信号的“克隆”版本。

CFG_HIT 表明一个有效的配置周期开始。

ADDR_VLD 表明当前作业地址线的起始地址有效。

S_SRC_EN 在Slave模式读操作期间,告诉用户模块驱动下一片数据到总线ADIO[31:0]上。

S_DATA_VLD 表明当前ADIO[31:0]上的数据为有效数据(在Slave模式下)。

BASE_HIT[7:0] 表明基地址寄存器译码并选中相应的PCI映射空间。

CFG[255:0] PCI设备配置空间接口信号。

M_SRC_EN 在写操作时,表明数据源可以驱动下一片数据到ADIO[31:0]上(在INItiator模式下)。

M_DATA_VLD 表明当前数据线ADIO[31:0]上的数据为有效数据(在Initiator模式下)。

REQUEST 在主设备模式下,DMA控制器请求系统仲裁器让出总线。

M_WRDN 在主设备模式下,当前的作业进行读操作或写操作。M_WRDN=1时表示写,M_WRDN=0时表示读。

M_DBE[3:0] 在主设备模式下,驱动总线命令和字节有效信号。

COMPLETE 在主设备模式下,当前的DMA方式传送数据完成。

M-DMTA 表示在Initiator模式下当前主设备正片于数据周期。

DR_BUS 表示主设备状态机正驱动PCI总线。

I_IDLE 表示主设备状态机正在空闲状态,当前PCI总线没有被驱动。

M_ADDR_USR 表示主设备状态机在地址周期要求驱动地址信号到ADIO[31:0]上。

RST PCI总线复位信号的“克隆”版本。

CLK 由系统缓冲区驱动的PCI总线时钟。

INTER_USR 由用户发出的中断请求信号。是INTR_A信号的“克隆”版本。

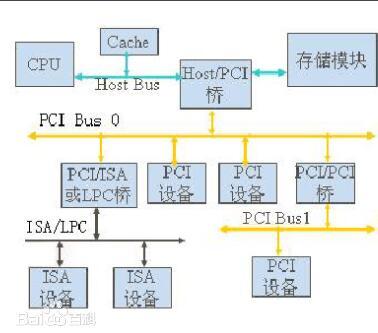

从LogiCore提供的接口看出,该软“核”将复杂的PCI接口按照PCI的两种工作模式转化成相对简单的Slave和Master两组独立接口信号。用户可以根据实际需要来确定的应用那种模式,从而选用相应的一组或两组信号作为接口。而且LogiCore这种桥梁作用只是对PCI功能进行划分,它将PCI控制器的核心逻辑留给用户来实现,并给出状态机的接口信号。

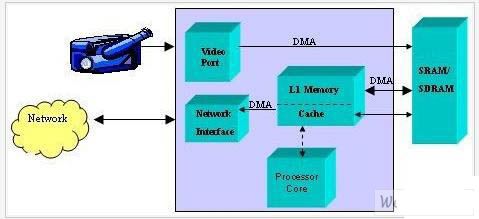

2 PCI Master控制器的实现

以一个基于PCI总线的数据采集卡为例说明利用LogiCore实现PCI Master控制器的方法。由PCI协议知道,当PCI设备工作在Master模式下,可以直接访问计算机系统主存储器,而不通过计算机CPU。为此,在PCI Master控制器中必须设计一个DMA控制器。这样同主存储器传送数据时,可以暂时接管系统总线,控制传送字节数,判断DMA传输是否结束,发出DMA结束等信号来保证数据的正确传送。该数据采集卡所实现的功能就是不断从外部接收数据并以DMA方式输入到计算机系统缓冲区中,同时将预先放在计算机内存中的大量数据以DMA方式输出到外部的仪器中。DMA控制器属于LogiCore逻辑框图中的用户控制模块。它由现行字节数寄存器、现行地址寄存器、基字节数寄存器、基地址寄存器、半满地址寄存器、全满地址寄存器、状态寄存器、读写缓冲器及控制寄存器和优先级编码器等组成、DMA控制器原理图如图3所示。其中控制寄存器和优先级编码器是DMA控制器的关键。

2.1 DMA控制器的特点

(1)现行地址寄存器、基字节数寄存器、基地址寄存器、半满地址寄存器、全满地址寄存器5个寄存器可由高层应用程序根据当前驱动程序分配的系统内存空间来灵活配置。当传送完规定的传送长度(字节数减到零时),结束当前DMA传送并自动重新对现行地址寄存器进行初始化,具有自动初始化能力。

(2)优先级编码器中的4个DMA请求源的优先级是固定的,不可以旋转。优先级按照从高到低依次为读缓冲器、STATUS_C(由状态寄存器C-D发出的)、写缓冲器、STATUS_D(由状态寄存器C-D发出的)。

优先权编码器对4个DMA请求源进行优先级编码,并向LogiCore发出DMA请求信号。

(3)DMA数据传送有单字节传送和数据块传送两种方式。数据块传送方式可由用户初始化基字节寄存器来灵活设置一次传送的数据块长度。DMA控制器向系统缓冲区发送状态寄存器C-D中的信息时采用单字节传送方式。而传送读缓冲器和写缓存器中的数据时采用数据块传送方式并可由用户设置一次传送数据的长度。此时每传送一个数据,地址指针加1,字节数据1。

(4)DMA控制器中读缓冲器和写缓冲器都是2KB。

2.2 DMA控制器基本工作原理

2.2 DMA控制器基本工作原理

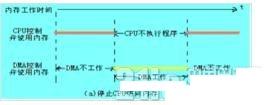

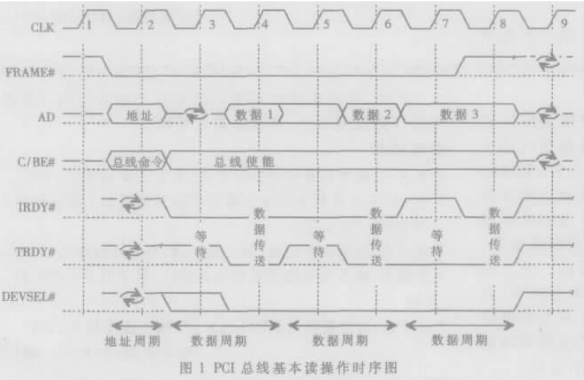

首先由高层应用程序根据采集卡的低层驱动程序分配的系统内存地址对基地址寄存器、半满地址寄存器、全满地址寄存器、状态寄存器、读写缓冲器和控制寄存器进行初始化。然后启动系统,开始工作。当读缓冲器的数据量不到半满或写缓冲器中接收到的数据量已超过半满或状态寄存器C-D有状态信息向高层报告时,则向优先级编码器发出相应的请求信号。DMA优先级编码器根据DMA请求对象的操作类型向DMA控制寄存器发出相应的控制信号。当DMA控制器检索到对应的控制信息发生变化时,向LogiCore发出DMA请求,并用基字节寄存器和基地址寄存器分别初始化现行字节数寄存器和现行地址寄存器。当计算机系统允许DMA控制器占用PCI总线时,则DMA控制器接管PCI总线,并在地址周期向LogiCore发出DMA读写命令,同时输出当前要对系统缓冲区操作的起始地址。在随后的数据周期中,从数据总线ADIO上输出或接收数据,同时修改地址指针(DMA支持隐含寻址)和字节计数器值,DMA控制器检测传送是否结束。如未结束则不停循环传送。当检测到字节计数器即将为零时,则向LogiCore发出COMPLETE信号,COMPLETE信号持续到字节计数器为零时,DMA控制器释放掉对PCI总线的控制权,使CPU恢复正常工作状态。

在DMA控制器中,状态寄存器C-D有两个DMA请求源STATUS_C和STATUS_D。其中STATUS_C在地址比较器检测到读缓冲器读完对应系统缓冲区一半空间或全部读守对应系统缓冲区数据时,置相应的状态信息并向优先级编码器发出STATUS_C请求信号。而STATUS_D在地址比较器检测到写缓冲器写完对应系统缓冲区数据、置相应的状态信息并向优先级编码器发出STATUS_D的请求信号。

值和注意的是,在DMA控制器设计过程中,当进行数据块传输、字节数寄存器计数快结束时,应提前向计算机系统发出完成本次数据块传送的COMPLETE信号,这样可保证DMA数据块传送的正确进行。至于提前几个字节数据可以根据试验来确定,一般提前2~4个字节即可。

PCI总线设计中定义的双向信号,均要用OE信号来控制。同时有些信号如地址比较等要进行分割,以使用最少的通用逻辑模块数来实现。这些是PCI总线设计所要注意的事项。由于LogiCore中对这些情况在逻辑上已经进行优化处理,从而使用户避免了同复杂的PCI接口打交道,减少犯错误的可能,缩短了开发周期。

本数据采集卡在WINDOWS 98多任务操作系统下运行数据传输速率可以达到140Mbps,满足了实际要求。

电磁炉相关文章:电磁炉原理

评论