基于NiosⅡ的超声电机驱动控制电路

1.2.1 NiosⅡ系统的搭建

Nios II是Altera公司开发的软核32位的RISC微处器,作为一个采用硬件描述语言编写的软核,Nios II可以通过内带的Avalon总线机制与其他采用HDL语言描述的硬件接口模块组成Nios系统一起嵌入到Altera的Stratix、Cyclone或APEX系列的FPGA中,从而构成一个可编程片上系统设计。

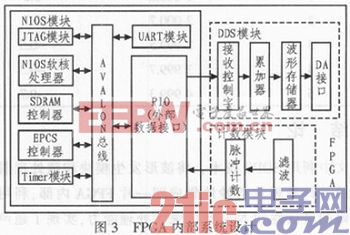

首先要构建一个基于Nios II的最小系统,这个系统的组件都在SOPC Builder提供的IP核中,依次选择Nios II处理器、EPCS控制器、SDR AM控制器、JTAG模块。其中,NiosⅡ实现MCU的功能,SDRAM和EPCS控制器组件用来连接外部存储器,JTAG模块实现程序的调试与下载。除此以外,我们还需要用到串口接收上位机发送来的数据以及定时器中断,因此在系统中添加UART模块和定时器模块。最后,处理器要控制DDS模块的运行并且接收光栅计数模块计算出的脉冲数,还需要添加一些I/O口用作数据的传输。这样,FPGA内部的一个NIOS系统就构建完成了。

1.2.2 DDS模块

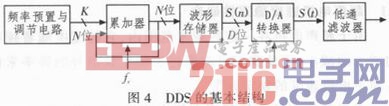

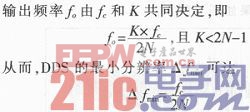

直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。基本原理是以数控振荡器的方式,产生频率、相位可控制的正弦波、余弦波、三角波、三角波、方波等波形。图4所示为DDS的基本结构。

图4中,fc为时钟频率,K为频率控制字,N为相位累加器的字长,D为ROM数据线宽度。

本文的DDS设计主要分为3个模块:控制字接收模块,用来与NIOS系统进行通信,接收来自上位机的控制字;波形存储器模块,用来产生驱动信号所需要的波形,本文只需要产生正弦波;相位累加器模块,用来产生频率和相位,本文是将接收到的频率和相位控制字转化为实际的频率和相位。

1.2.3 脉冲计数模块

脉冲计数模块由滤波和计数两部分构成,主要是为了读取光栅编码器反馈回来的信息,从而实现对电机的精确定位和速度控制。本文使用的光栅编码器,其分辨率为0.5um/count,输出A+/A-、B+/B- 2路差分信号,为将编码器的差分输出转换成单端脉冲信号,本文选用了26LS32AC差分转单端芯片实现差分信号的转换。转换后的两路信号A、B是一组正交脉冲信号,电机朝不同方向运动时,A、B两路信号之间

的相位关系会发生转换,从而判断电机运行的方向。因此,根据这一特性,在FPGA中,用Vetilog语言编写了一个实现正交编码脉冲电路的功能的计数模块。

同时,为了进一步消除光栅反馈信号可能产生的窄脉冲干扰信号,本控制器将转换后的单端信号进一步滤波。主要过程是:在采集某一状态信号时,利用比该状态信号更高频率的采样时钟对其进行多次重复采集,直到多次采集结果完全一致时才视为有效信号输出。然后再将滤波过后的信号发送给正交编码脉冲电路进行辨向和计数。

1.3 驱动控制器的控制方式

电机工作时,FPGA通过串口接收来自上位机发送的数据至Nios II处理器中,经过程序处理之后,得出电机运行的方式(步进、连续)、运行的距离等信息,NiosⅡ处理器通过控制DDS模块的起停时间来控制驱动信号的有无进而控制电机的运动过程。电机运行时的位移和速度的实际信息可以从光栅编码器的反馈信号中得出,计数器模块计算出脉冲数的值发送给Nios II处理器,处理器通过具体的控制算法改变DDS输出信号的幅值、频率、相位从而对电机的运行状态做出进一步的调整。这样,一个完整的闭环控制系统就由一块FPGA芯片实现了。

评论