基于S3C4480X的大翟LED显示系统设计

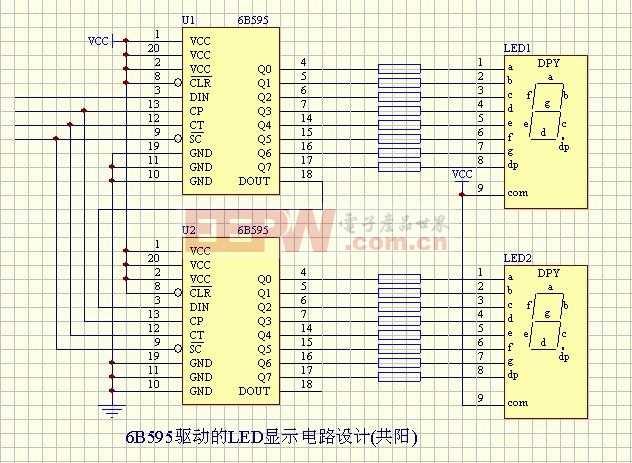

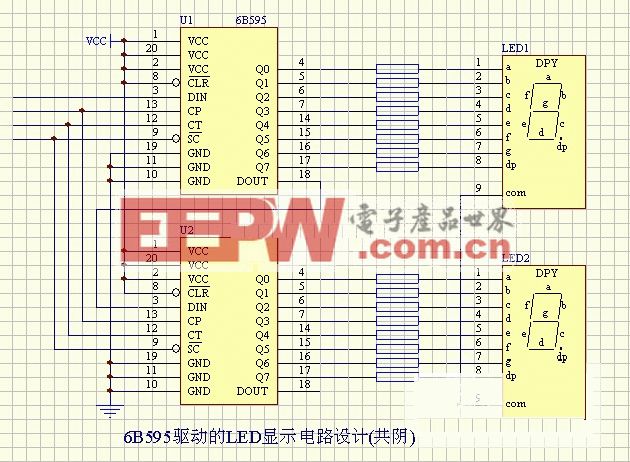

1.2 主控电路与LED屏的接口设计

本显示系统选用基于ARM7TDMI内核并带有内部DMA控制器的S3C44BOX作主控制器,使其工作在ARM状态,并使用16位总线。由于把LED屏虚拟的视为一段连续的存储单元,故为其分配地址空间0x2000000~Ox4000000。

主控电路与I。ED屏接口应能实现以下功能:

◆选通任意位置的显示模块及该模块上的第一级列数据锁存器。将该位置要显示的点阵码准确锁存,并能在第一级列数据锁存器数据刷新后,将刷新数据锁存到第二级列数据锁存器并输出。

◆能控制选通驱动16行同名行中的一行进行逐行扫描显示。

◆实现主控芯片3.3 V到LED屏5 V的逻辑电平转换。

主控板与LED屏接口电路原理图如图2所示。

一个大型LED屏的结构可分为纵向级联和横向级联,这种结构类似于一个三维数组。假设一个三维数组LED[i][j][k]其中:

i=O,1,2…,m表示LED屏纵向级联级的序号。

j=O,l,2…n 表示LED屏横向级联级的序号。

k=O,1,2….,16 表示显示模块上16个第一级列数据锁存器的序号。

由于系统使用16位并行总线数据传输方式,并将LED屏视为一段连续的存储单元,故使用A[4:1]作显示模块上选通第一级列数据锁存器译码器(图1中u2)的译码输入,即为三维数组的k变量;使用A[8:5]作选通横向级联显示模块的译码器(图2中U7)译码输入,即为三维数组的j变量;由于LED屏要具有良好的灵活性,又由于采用DMA传输数据要求点阵码存放顺序的技术要求,纵向级联级选通不满足使用地址总线译码选通的条件,所以使用S3C44BOX的PG[2:0]作纵向级联级选通译码器的译码输人,即三维数组的i变量。

由于地址和数据总线上的状态不断变化,所以在对LED屏进行写操作时,地址和数据信号应进行锁存,主控板上分别使用U2、U3和U4锁存对LED写操作时的地址和数据总线的状态。LED屏分配首址为0x2000000,当对其进行写操作时,S3C44BOX的nGCSl和nWE脚会出现可编程控制时延的有效低电平。nGCSl经一个非门作U2、U3和U4的锁存使能控制信号,保证仅在对LED屏访问时,地址和数据总线上的信号才被锁存。nWE经一个非门作屏端第一级列数据锁存器(图1中U3~U19)的锁存使能控制信号,保证只有当刷新数据稳定出现在列数据锁存其输入端时才被锁存。S3C44BOX的PCl0作所有屏端第二级锁存器(图l中U20~U35)的锁存使能控制信号线;S3C44BOX的PC[3:O]作16行驱动译码器(图l中U1)的译码输入。由于数据传输时只需要主控板对LED屏输出控制,不需要信号反馈,所以接口电路采用廉价的5 V供电的HCT电路芯片方案,就可满足主控芯片3.3 V到LED屏5 V的逻辑电平转换。

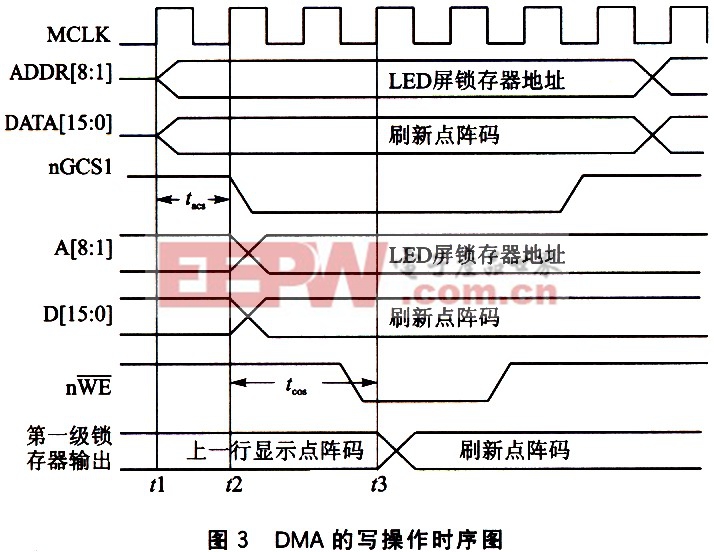

在DMA传输数据时,更关心的是DMA的写操作,时序如图3所示。t1时刻DMA写操作开始,地址和数据总线上出现I,ED屏相应位置的地址和刷新数据;t2时刻nGCSl引脚出现有效低电平,地址和数据总线上的数据被锁存到U2~U4并输出;t3时刻nWE引脚出现有效低电平,u2~u4的输出数据被锁存到屏端第一级列数据锁存器并输出。这样主控制器就完成了一次列数据的刷新。

2 软件设计

2.1 LED屏显示程序设计

由于使用了S3C4480X内部DMA控制器进行数据的传输与控制,显示程序得到很大简化,程序流程如图4所示。点阵码的传输全由DMA控制器完成,只需在启动DMA数据传输前将点阵码的首址、LED屏的首址及传输数据量的值分别赋给相应的控制字后,启动DMA操作即可。完成所有本同名行点阵码传输后,将刷新的数据锁存到第二级列数据锁存器输出,并驱动本同名行显示。这样循环显示16行同名行后就完成了一帧点阵显示。

评论