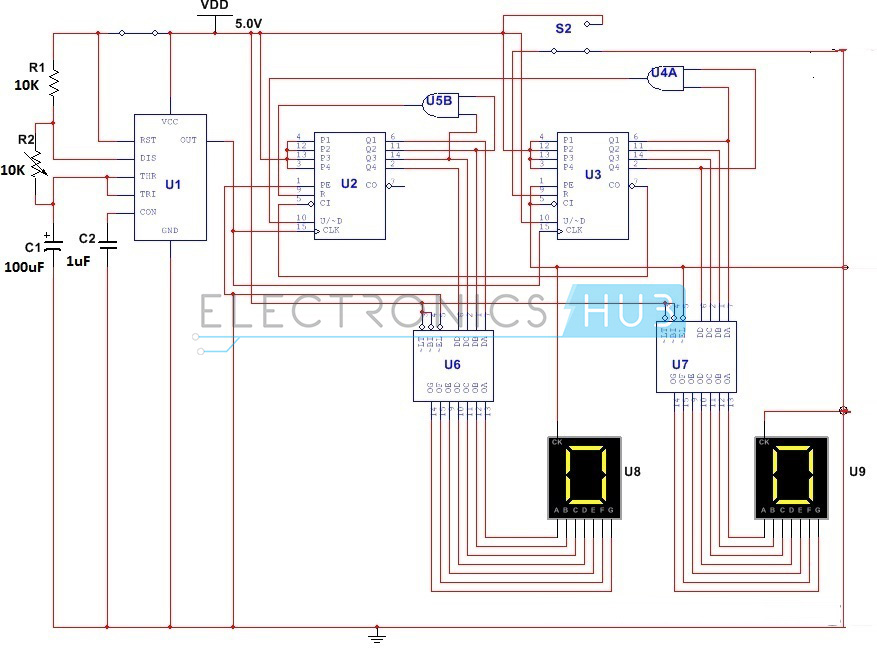

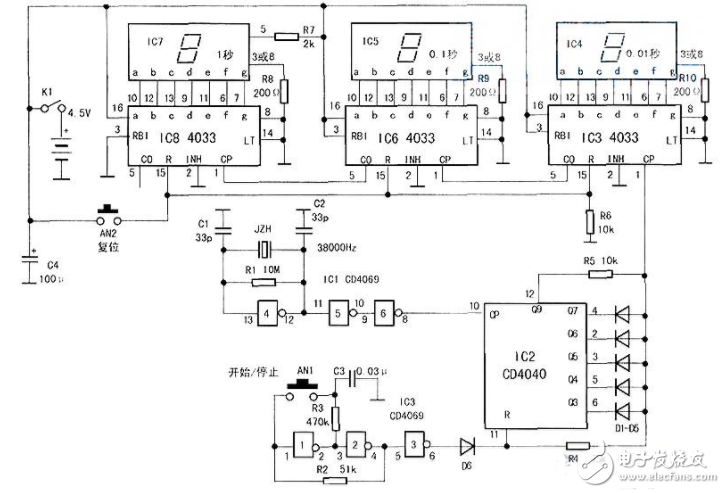

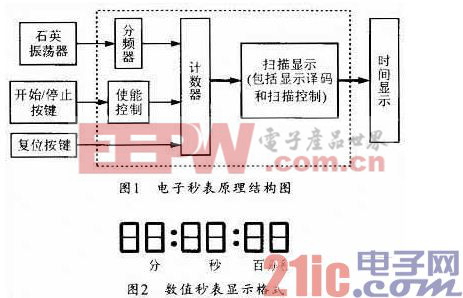

数字秒表电路设计

二、设计依据

本电路主要采用了二输入与非门74LS00,十进制BCD码计数器74LS160,BCD七段译码器/驱动器7447,555时基集成电路,七段数码管。

利用74LS00可以组成RS触发器,单稳态触发器。其74LS00的逻辑功能是有0出1,无0出0。

其逻辑表达式:Y=/(AB) ,真值表如下:

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

十进制BCD码计数器74LS160具备计数分频功能,其真值表如下:

输入 | 输出 | |||||||||||

CLK | CLR | LOAD | EP | ET | A | B | C | D | QA | QB | QC | QD |

X | 0 | X | X | X | X | X | X | X | 0 | 0 | 0 | 0 |

↑ | 1 | 0 | X | X | A | B | C | D | A | B | C | D |

X | 1 | 1 | 0 | X | X | X | X | X | 保持 | |||

X | 1 | 1 | X | 0 | X | X | X | X | 保持 | |||

↑ | 1 | 1 | 1 | 1 | X | X | X | X | 加法计数 | |||

↑ | 1 | 0 | X | X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

逻辑功能:当CLR,LOAD,EP,ET均接高电平时,时钟CP端每来一个上升沿,计数器在原来的基数上加1,并从QA,QB,QC,QD,输出相应的十进制BCD码。利用74LS160的这个功能特点可以设计出十分频器,计数器。

7447为BCD七段译码器/驱动器,真值表如下:

十进制 | LT | RB | D | C | B | A | BI/RBO | a | b | c | d | e | f | g |

0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

1 | 1 | X | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

2 | 1 | X | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

3 | 1 | X | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

4 | 1 | X | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

5 | 1 | X | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

6 | 1 | X | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

7 | 1 | X | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

8 | 1 | X | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

9 | 1 | X | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

7447为四线-七段译码器,可以用来驱动七段共阳极数码管,当LT,RBI,BI,端接高电平时,从DCBA端输入BCD码时,从abcdefg端输出相应的数码管显示码。

共阳七段数码管真值表

A | B | C | D | E | F | G | 显示字符 |

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

0 | 0 | 1 | 0 | 0 | 1 | 0 | 2 |

0 | 0 | 0 | 0 | 1 | 1 | 0 | 3 |

1 | 0 | 0 | 1 | 1 | 0 | 0 | 4 |

0 | 1 | 0 | 0 | 1 | 0 | 0 | 5 |

1 | 1 | 0 | 0 | 0 | 0 | 0 | 6 |

0 | 1 | 1 | 1 | 1 | 1 | 7 | |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 8 |

0 | 0 | 0 | 1 | 1 | 0 | 0 | 9 |

结合四线-七段译码器7447可以现实0到9个数字。

分频器相关文章:分频器原理 脉冲点火器相关文章:脉冲点火器原理

评论