多锁相环和扩频时钟在数字娱乐设备中的设计应

1. 高清电视系统中采用多种频率的需要——不同的标准和接口

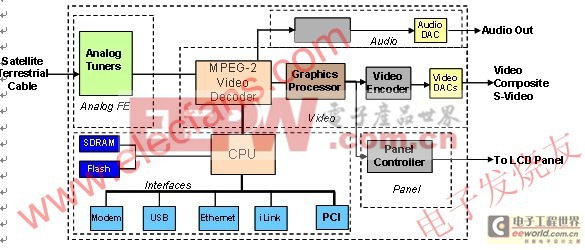

图1所示为液晶电视机天线的基本原理图,简单地说明了数字电视将输入的数字数据流处理成适于用户起居室内电视机使用的正确音频和视频格式的流程。

Satellite Terrestrial Cable卫星地面电缆

Analog Tuners模拟天线

Analog FE模拟前端

MPEG-2 Video DecoderMPEG-2视频解码器

MPEG Audio DecoderMPEG 音频解码器

Audio DAC音频数模转换器

Audio音频

Audio out音频输出

Graphics Processor图形处理品

Video Encoder 视频编码器

Video DACs视频数模转换器

Video Composite S-Video视频复合S-Video端子

Video视频

Flash闪存

Panel controller面板控制器

To LCD Panel接至液晶显示屏

Panel显示屏

Interface接口

Modem 调制解调器

图1:常见液晶电视机体系架构

调谐电路板上加入了多个子系统。各项基本功能从广义上可以归类到以下几种模块下:

1.模拟前端(解调器)

2.音频/视频编码和解码(MPEG视频解码器/MPEG音频解码器)

3.各类接口

4.显示屏

上图中所显的所有模块几乎都需要时钟信号。CPU要求的时钟信号典型范围为30 – 100MHz。MPEG标准要求采用基于27MHz的时钟输入。其中存在需要解码器和编码器同步的必要功能,而这项功能由VCXO(电压控制晶体振荡器)来实现。对于作为数模转换器(DAC)时钟源的音频时钟,其ppm要求极为严格。这些频率取决于采样频率和过采样比率。对于各类接口来说,时钟信号由各自的标准来决定,诸如USB、以太网、调制解调器、PCI、PCIExpress、SATA等等。

显示屏的时钟取决于屏幕尺寸以及显示标准(高清(HD):1080i、1080p、720p;标清(SD):NTSC、PAL)。屏幕控制器子系统的基本系统是将输入图像数据转换成实际屏幕尺寸,例如,采用74.17582418 MHz等时钟。

2. 电视机体系架构和时钟树的实现

目前,设计者不得不在设计前期做出的一项关键决定就是信号格式,包括模拟信号或数字信号。几年以前,电视机的信号链路还是主要以模拟信号为基础,而如今,更为常用的是数字音频数据通路。数字和模拟通路均各自存在着一些固有的优缺点。但是,目前存在着一种全球性的必然发展趋势,即要求所有信号传输都采用数字技术,该趋势将分阶段实现。

高清电视的传输采用了数字信号,所以,新出品的电视机趋向于采用数字通路。采用数字传输方式的优点在于对噪声的容错性很高。另一方面,模拟信号易受到噪声的影响。电路板设计者需要在布线时加特别关注,采用拥有更优信噪比(SNR)性能的差分信号,或者运用屏蔽技术来避免信号品质降低。

传统的时钟树设 计方式:这种方式针对每一种频率要求采用了分立的晶体/晶体振荡器(XO)。这种方式的好处在于,时钟可以布置在非常靠近元器件的位置,使布线变得简洁。但是,这种方式的缺陷在于,每一个晶体/晶体振荡器元件都必须提前从供货商处采购,从而不允许在最后阶段做出设计变更。如果有一个频率发生了变化,也要求有很长的交货周期,从而导致整个进度的延迟。

硅芯片时序解决方案:近10多年以来,基于锁相环的时序解决方案的流行度已经超过了传统时钟方法。硅芯片时序解决方案供货商能够提供分立晶体和晶体振荡器元件所不支持的多项功能,从而可应用于复杂的系统设计。这两种设计方式之间的折衷处理将在下文进行讨论。转向采用这种体系架构的客户所获得的主要益处在于,它赋予了客户的设计方案灵活性并节省了成本。

3. 与分立晶体/晶体振荡器相比,采用锁相环硅芯片时序解决方案的优势

1.成本——消费类产品市场领域的重要决策的驱动要素之一就是成本。每一次体系架构的变动都必须经济而划算,这样才可以实施架构转变,所付出的投资才是合理的。硅芯片时序解决方案最具吸引力的优势在于,通过将若干个晶体/晶体振荡器集成到一起,可以降低整体物料清单成本,并保持性能水平,或在某些情况下提升性能水平。在如上图所示的典型电视机天线电路板中,采用了5-6个分立晶体(每个成本为0.12 – 0.50美元),而如果一个能够提供上述频率的可编程功能的硅芯片时钟发生器的成本低于2.00美元,则就会真正为电路板增值。除了成本是晶体/晶体振荡器集成的主要推动要素,另外还有一些能够为OEM商和最终用户所感受到的其它优势。

2.可靠性——晶体是基于石英的元器件,比起基于锁相环的时序解决方案来说,晶体的故障率较高。从系统中每减少一个晶体都有助于提高整个系统的可靠性。集成度高还能够减少电路板上的元器件数量,获得最高的稳定性并实现更低的返修率。

3.晶体可用性——频率范围在10-40 MHz之间的晶体很容易做到。但高于40 MHz以上的高频晶体在制造上难度更高并且需要采用特殊的制造技术。这种晶体属于高阶泛音晶体,成本范围在1-10美元之间。这些高阶晶体较难购得。而硅芯片时序解决方案能够采用单个低频晶体(或者可以使用时钟基准信号)来生成多个高频输出。

4.晶体老化——晶体本身容易出现老化现象,每隔几年会出现+-2ppm至+-5ppm的误差。这种老化现象的原因在于晶体材质内部以及晶体表面之上存在的杂质以及晶体材料与沉积电极之间的机械应力。老化可能导致使用晶体的系统性能缓慢下降。在使用晶体时,长期频率漂移已经成为常见的问题。而基于锁相环的硅芯片时序解决方案能够在产品整个使用寿命内保持精确度。

5.可编程性——基于锁相环的时钟发生器拥有内置可编程性,可以在设计阶段提供一定的灵活性。这些可编程特色不仅包括了输出频率的改变,而且能够改变驱动信号强度设置值、扩频百分比、通过引脚编程实现频率选择,这些意味着同一个输出端可以根据需要提供不同的频率。系统内置的可编程性可以采用串行I2C接口在设计执行过程中改变一些特定参数。这一特色对于那些在多个平台上采用同一组频率的制造厂商是富有吸引力的。

6.减少元器件数量,节约板卡空间——采用可编程时钟发生器有助于通过集成减少电路板上的元器件数量。系统设计者正在趋向于采用更少的元器件,以求减少由于布线和需要保持信号完整性所带来的问题。基于锁相环的时钟发生器能够采用一个低频晶体生成若干个输出,因此对于减少元器件总数量以及节约宝贵的板卡空间极具价值。

7.采用扩频时钟降低电磁干扰——电视机天线电路板典型情况下为5-7层板,并采用了专用的铺地层以便压低干扰。为提高系统性能和避免发生串扰、扭曲和信号完整性问题,要对多路高速信号进行精心的布线。而硅芯片时序器件供货商通过提供扩频等功能,减少了这些板卡设计方面的问题。例如,扩频可以通过扩展高速信号来降低信号的峰值能量。

电磁干扰必须低于强制性标准所规定的限值,这些标准如CISPR 22或FCC Part 15 Class B。所有消费类产品必须通过严格的FCC规范认证才能上市。全球各地诸如美国通信委员会(FCC)这样的管理机构会确保强制性标准得到遵守而且器件产品不能在不属于它们的频段内发射信号。不幸的是,存在频率谐波的高速设计方案经常会遇到这方面的问题。扩频是一项目前由集成电路供货商提供的、能够解决这一干扰问题的功能。

扩频功能能够减少、甚至消除对会增加物料清单成本的铁氧体磁珠、滤波器、线圈和振流器的需要。如果系统未能通过电磁合规试验,则需要花大力气进行重新设计。考虑到试验所耗费的成本以及重新进行工程设计所浪费的时间,我们会 认识到对这些问题做好通盘考虑并采取保险措施的重要性,例如提前采用扩频功能。而拥有可编程性就可以在需要时打开扩频功能以及在不需要时关闭该功能。这一功能在开发和测试中尤为实用。

8.库存管理——采购团队目前所面临的一项主要难题是对系统采用的每

评论