ADV202编解码芯片介绍

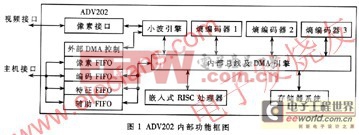

ADV202的内部功能框图如图1所示,输入的视频或图像数据进入视频接口后经过解交错传输到小波变换引擎中。在小波引擎中,每帧图像或每个图 块通过5/3或9/7滤波器分解成许多子带,生成的小波系数写入内部寄存器中。熵编码器将图像数据编码为符合JPEG2000标准的数据。内部DMA引擎 提供存储器之间的高带宽传输以及各模块和存储器之间的高性能传输。内部FIFO提供像素数据、码流数据、特征数据和辅助数据的存储空间,既可由外部主机通 过标准地址读写周期直接访问,也可以采用DREQ/DACK协议通过DMA方式访问或专用硬件握手机制访问。主机接口提供16/32位的控制总线和 8/16/32位的数据传输总线,用于对内部寄存器的配置、控制和状态传递以及压缩数据流的传输。

评论