ML2036型串行接口正弦波发生器及其应用

——

在许多测试电路中往往需要产生频率和幅度连续可调的过零正弦波信号,近年来dds(数字直接频率合成)技术比较迅速,广泛应用于通信领域,快速达到几百兆甚至上千兆,这里仅介绍一款适合信号测试电路的低成本dds-ml2036,其电路更为简洁实用。

2 ml2306的主要特点

ml2306的主要特点如下:

可编程输出频率dc-50khz。

正负双电源供电,过零正弦波输出。

低增益误差和谐波失真。

3线spi兼容串行微控制器接口。

完全整合解决方案,无需外部元件。

12mhz的时钟输入时频率输出分辨率1.5hz(±0.75hz)。

集成3mhz-12mhz晶体振荡电路。

输入时钟频率的1/2或1/8时钟输出。

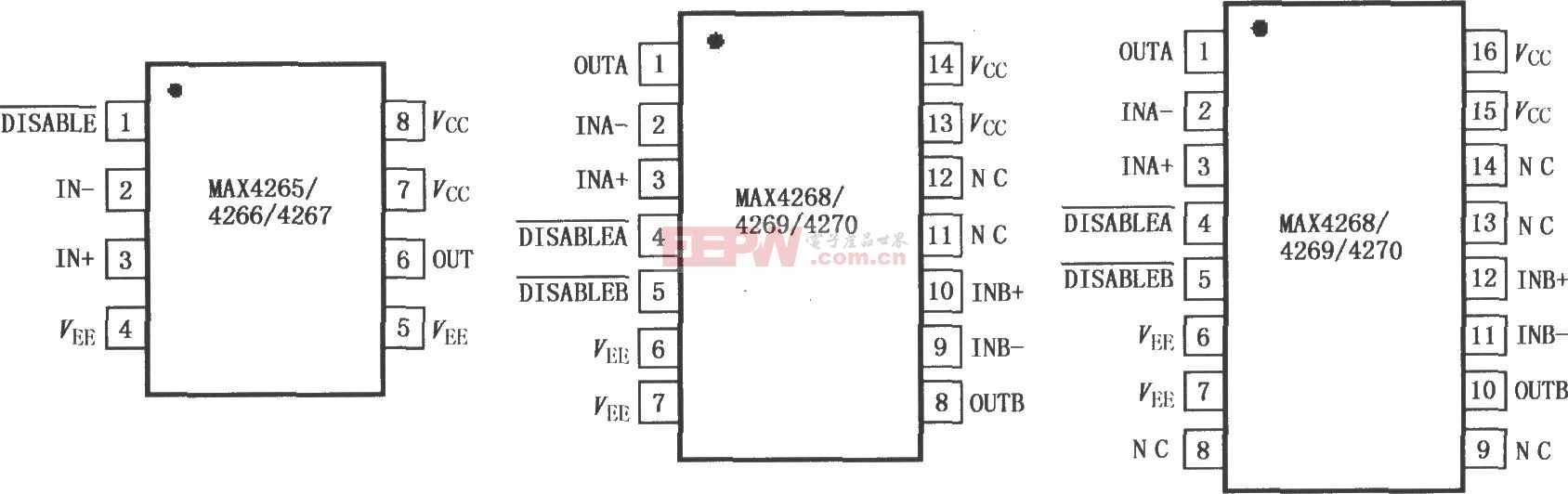

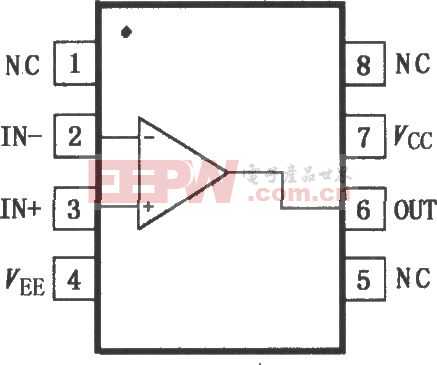

ml2306采用pdip和soic两种封装,引脚排列如图1所示,各引脚功能如表1所列(圆括号内的引脚号为soic封装)。

3 ml2306基本原理

3 ml2306基本原理 ml2306由可编程频率发生器、正弦波发生器、晶体振荡器和串行数字接口组成。

3.1 频率发生器

可编程频率发生器通过16位数据字产生频率稳定的数字输出。频率发生器是由fclkin/4时钟控制的相位累加器组成,每4个clkin周期存储在数据锁存器中的数据加到相位累加器,输出频率等于累加器溢出率。当fclkin=12.352mhz时,δfmin=1.5hz(±0.75hz),通过使用一个低输入时钟频率可以获得较高分辨率的频率输出。例如当fclkin=1mhz时,δfmin=0.12hz(±0.06hz)。

输出频率:fout=fclkin(d15-d0)dec/223

频率分辨率:δfmin=fclkin/223

3.2 正弦波发生器

正弦波发生器由正弦查找表、dac和低通滤波器组成。正弦查找表存储有正弦波的量化数据,在时钟控制下循环输出这些量化数据驱动数模转换dac产生阶梯正弦波,再经过低通平滑滤波器便可产生平滑的正弦波。

ml2036有一个基准电压vref输入。当增益控制gain输入逻辑1时,vout正弦波峰峰值电压等于±vref,vref=0v-(vcc-1.5v);当gain输入逻辑0时vout峰峰值电压等于±vref/2,vref=0v-vcc。

模拟输出vout的零点偏移电压vos是峰峰值输出电压的函数,如果vout(p-p)=2.5v,vout(max)=±50mv,则vos(max)=±[(2.5+vout(p-p))/100]。

3.3 晶体振荡器

晶体振荡器为可编程频率发生器产生一个精确的参考时钟,可以在clkin和dgnd之间放置一个3mhz-12.352mhz的晶体,不需要其他外部电容或元件,也可以直接用0-12mhz的外部时钟驱动clkin。bl2036还有两个时钟输出用于驱动其他外部器件,clkout1是从clkin的2分频输出,clkout2是从clkin的8分频输出。

3.4 串行数字接口

串行数字接口由一个移位寄存器和数据锁存器组成,时钟输入信号sck、数据输入信号sid和数据锁存信号lati可以与任何微处理器方便接口。数据线sid上的串行16位数据字在串行移位时钟sck上升沿进入16位移位寄存器,数据装载到移位寄存器后在lati下降沿锁存,lati下降沿应该出现在sck低电平期间,时序如图2所示。

3.5抑制模式和掉电模式

3.5抑制模式和掉电模式 ml2036具有抑制模式和掉电模式,设置情况如表2所列。如果pdn-inh是逻辑1,通过在移位寄存器所有位插入0,同时使lati变为逻辑1且保持为高电平,器件进入掉电模式,在这种状态下,功率消耗减少到11.5mw最大值,vout输出为0v。也可以通过pdn-inh引脚变为逻辑0使ml2036进入掉电模式,而无需考虑移位寄存器内容和lati状态。如果使pdn-inh引脚变为vss-(vss+0.5v),同时把移位寄存器所有位插入0并把lati引脚变为逻辑1,器件进入抑制模式,vout将完成最后半个正弦波周期后接近vos范围,就如同没有电压输出一样,如图3所示。

4 应用电路

4 应用电路 ml2036简单易用,可以很方便的产生程控正弦波信号,图4所示是ml2036产生程控增益正弦波的硬件原理设计,图中的u3(ad5262)是程控数字电位器,具有256个节点,正负双电源供电,可以处理正负双向交流信号,过零正弦波峰峰值(±2.5v)分辨率可以达到vref/256=10mw,再经过运放把峰峰值放大为20v。单片机at89c2051用普通i/0口即可模拟ml2036和数字电位器ad5262的数字接口,从而对输出正弦波进行频率和幅度的控制。再把单片机串口收发信号经232电平转换后接到pc机串口,就构成幅度和频率都可以连续程控的过零正弦波信号发生器。

评论