ADC信噪比的分析及高速高分辨率ADC电路的实现

在雷达、导航等军事领域中,由于信号带宽宽(有时可能高于10mhz),要求adc的采样率高于30msps,分辨率大于10位。目前高速高分辨率adc器件在采样率高于10msps时,量化位数可达14位,但实际分辨率受器件自身误差和电路噪声的影响很大。在数字通信、数字仪表、软件无线电等领域中应用的高速adc电路,在输入信号低于1mhz时,实际分辨率可达10位,但随输入信号频率的增加下降很快,不能满足军事领域的使用要求。

本文引用地址:https://www.eepw.com.cn/article/20833.htm针对这一问题,本文主要研究在不采用过采样、数字滤波和增益自动控制等技术条件下,如何提高高速高分辨率adc电路的实际分辨率,使其最大限度地接近adc器件自身的实际分辨率,即最大限度地提高adc电路的信噪比。为此,本文首先从理论上分析了影响adc信噪比的因素;然后从电路设计和器件选择两方面出发,设计了高速高分辨率adc电路。经实测表明,当输入信号频率为0.96mhz时,该电路的实际分辨率为11.36位;当输入信号频率为14.71mhz日寸,该电路的实际分辨率为10.88位。

1 影响adc信噪比因素的理论分析

adc的实际分辨率是用有效位数enob标称的。不考虑过采样,当满量程单频理想正弦波输入时,实际分辨率可用下式表示:

enob=[sina0(db)-1.76]/6.02 (1)

式中,sinad表示adc的信噪失真比,指adc满量程单频理想正弦波输入信号的有效值与adc输出信号的奈奎斯特带宽内的全部其它频率分量(包括谐波分量,但不包括直流允量)的总有效值之比。

adc的信噪比snr,指adc满量程单频理想正弦波输入信号的有效值与adc输出信号的奈奎斯特带宽内的全部其它频率分量(不包括直流分量和谐波分量)总有效值之比。

由此可知,当adc的总谐波失真thd一定时,有效位数enob取决于snr;adc的snr越高,其有效位数enob就越高。下面就来分析影响adc信噪比snr的因素。

理想adc的噪声由其固有的量化误差(也称为量化噪声,如图1所示)产生。但实际使用的adc是非理想器件,它的实际转换曲线与理想转换曲线之间存在偏差,表现为多种误差,如零点误差、满度误差、增益误差、积分非线性误差inl、微分非线性误差dnl等。其中,零点误差、满度误差、增益误差是恒定误差,只影响adc的绝对精度,不影响adc的snr。inl指的是在校准上述恒定误差的基础上,adc实际转换曲线与理想转换曲线的最大偏差。而dnl指的是adc实际量化间隔与理想量化间隔的最大偏差,改变adc的量化误差,能更直接地计算出adc实际转换曲线与理想转换曲线的偏差对adc的snr的影响。

非理想adc,除了上述误差外,还有各种噪声,如热噪声、孔径抖动。前者是由半导体器件内部分子热运动产生的,后者是由adc孔径延时的不确定性造成的。而adc的外围电路同样会带来噪声,如adc输入级电路的热噪声、电源/地线上的杂波、空间电磁波干扰、外接时钟的不稳定性(导致adc各采样时钟沿出现时刻不确定,带来孔径抖动)等,可以把它们都等效为adc的上述两种内部噪声。

非理想adc,除了上述误差外,还有各种噪声,如热噪声、孔径抖动。前者是由半导体器件内部分子热运动产生的,后者是由adc孔径延时的不确定性造成的。而adc的外围电路同样会带来噪声,如adc输入级电路的热噪声、电源/地线上的杂波、空间电磁波干扰、外接时钟的不稳定性(导致adc各采样时钟沿出现时刻不确定,带来孔径抖动)等,可以把它们都等效为adc的上述两种内部噪声。

上述误差和噪声的存在,导致adc的snr下降。下面先给出理想adc的snr计算公式,然后具体分析微分非线性误差dnl、孔径抖动△tj和热噪声对adc的snr的影响。

1.1理想adc的snr

理想adc的量化误差g(υ)与满量程内输入信号的电压v的关系如图1所示。量化误差为在[-q/2,q/2]内均匀分布且峰-峰值等于q(q=1lsb,lsb表示理想adc的最小量化间隔)的锯齿波信号。

设n位adc满量程电压为±1v,输入信号为s(t)=sinωt,则输入信号电压有效值vs=1/√2=2n/2√2×q,量化噪声电压有效值于是得adc输出信噪比为

snr=6.02n+1.76(db)

1.2微分非线性误差dnl

非理想adc的量化间隔是非等宽的,这将导致adc器件不能完全正确地把模拟信号转化成相应的二进制码,从而造成snr的下降;且adc每个量化的二进制码所对应的量化间隔都不同,为便于分析,用ε(lsb)= εq表示实际量化间隔与理想量化间隔误差的有效值,并近似认为由于dnl的影响,在无失码条件(dnl<1lsb)下,量化误差均匀分布在[-上q+εq/2,q+εq/2]和[-q-εq/2,q-εq/2]内。如图1 中实线所示(虚线伪理想adc量化误差)。这样,在考虑了dnl之后的adc量化噪声电压vq_dnl为:

1.3 孔径抖动△tj

1.3 孔径抖动△tj

孔径时间又称孔径延迟时间,是指对adc发出采样命令(采样时钟边沿)时刻与实际开始采样时刻之间的时间间隔。相邻两次采样的孔径时间的偏差称为孔径抖动,记作△tj。孔径抖动造成了信号的非均匀采样,引起了误差,设adc满量程电压为±1v输入信号为s(t)=sinωt,孔径抖动有效值为σ△tj,则由孔径抖动带来的误差电压为:

1.4热噪声

1.4热噪声

这里将adc电路中微分非线性误差dnl、孔径抖动△tj外的其它噪声都等效为adc输入端的热噪声电压vtn,设其有效值为σtn。

1.5非理想adc的snr

一般情况下,量化噪声、微分非线性误差dnl、孔径抖动△tj和热噪声彼此相互独立,综合芍虑这四个因素的影响,可得到adc的snr计算公式如卡:

式中,n--adc的量化位数ε--adc的实际量化间隔与理想量化间隔误差的有效值,单位lsbfin--adc输入信号频率,单位hzσ△tj--adc的孑l径抖动有效值,单位sσtn--等效到adc输入端的热噪声的有效值单位lsb

式中,n--adc的量化位数ε--adc的实际量化间隔与理想量化间隔误差的有效值,单位lsbfin--adc输入信号频率,单位hzσ△tj--adc的孑l径抖动有效值,单位sσtn--等效到adc输入端的热噪声的有效值单位lsb

对于高分辨率adc器件,其固有量化误差、微分非线性误差dnl和器件热噪声均较小。当fin较高时,adc电路的snr主要取决于孔径抖动,此时有

2基于ad6644ast一65的高速高分辨率adc电路设计实例

2基于ad6644ast一65的高速高分辨率adc电路设计实例

电路设计目标:有效位数enob≥10.50bit、采样率为40msps、输入信号频率小于15mhz,输入信号幅度为-ldbfs。该指标能满足数字仪表、高速数据采集卡、软件无线电和雷达、导航等领域中数字波束形成的要求。

2.1电路设计与器件选择

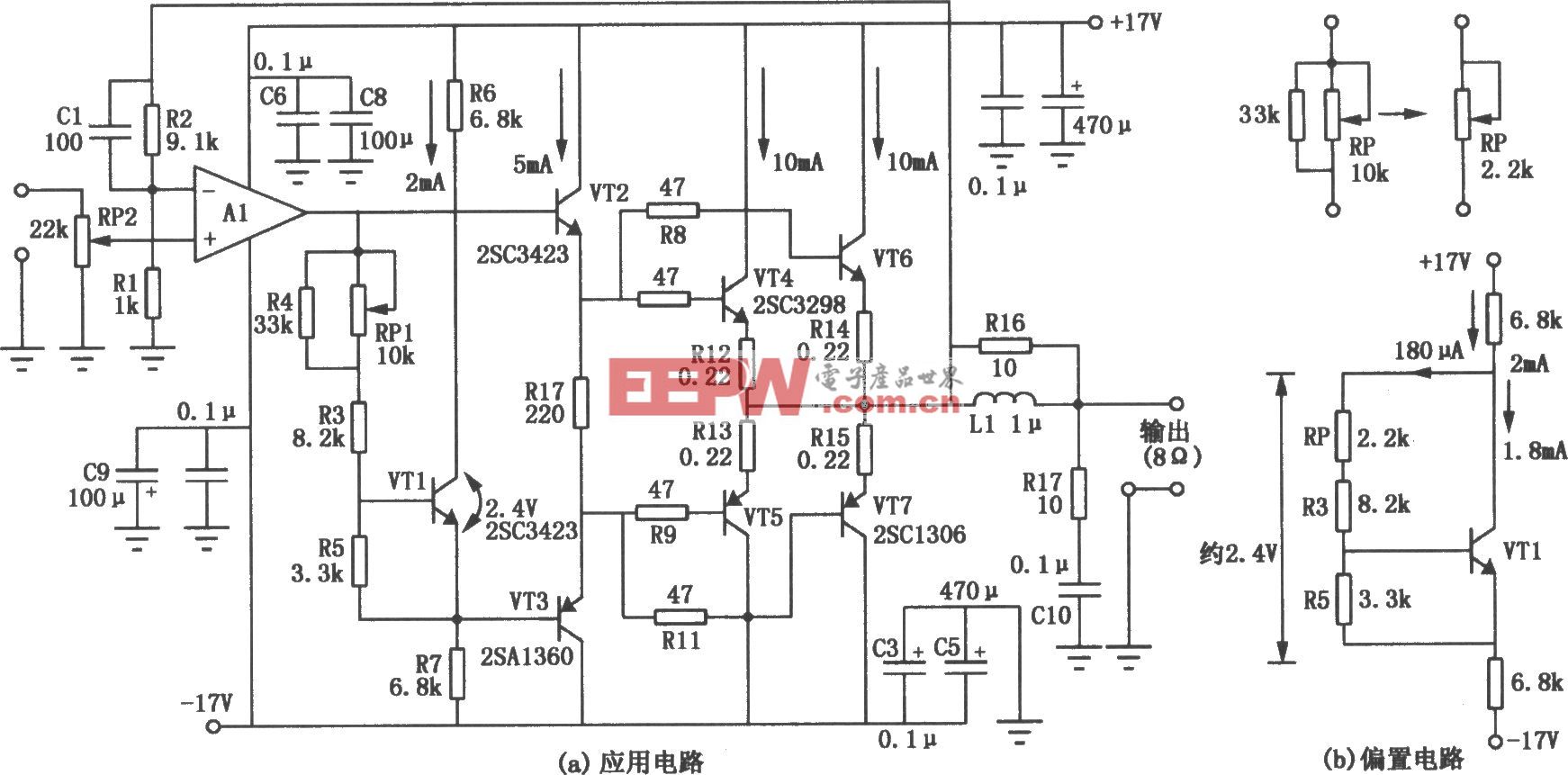

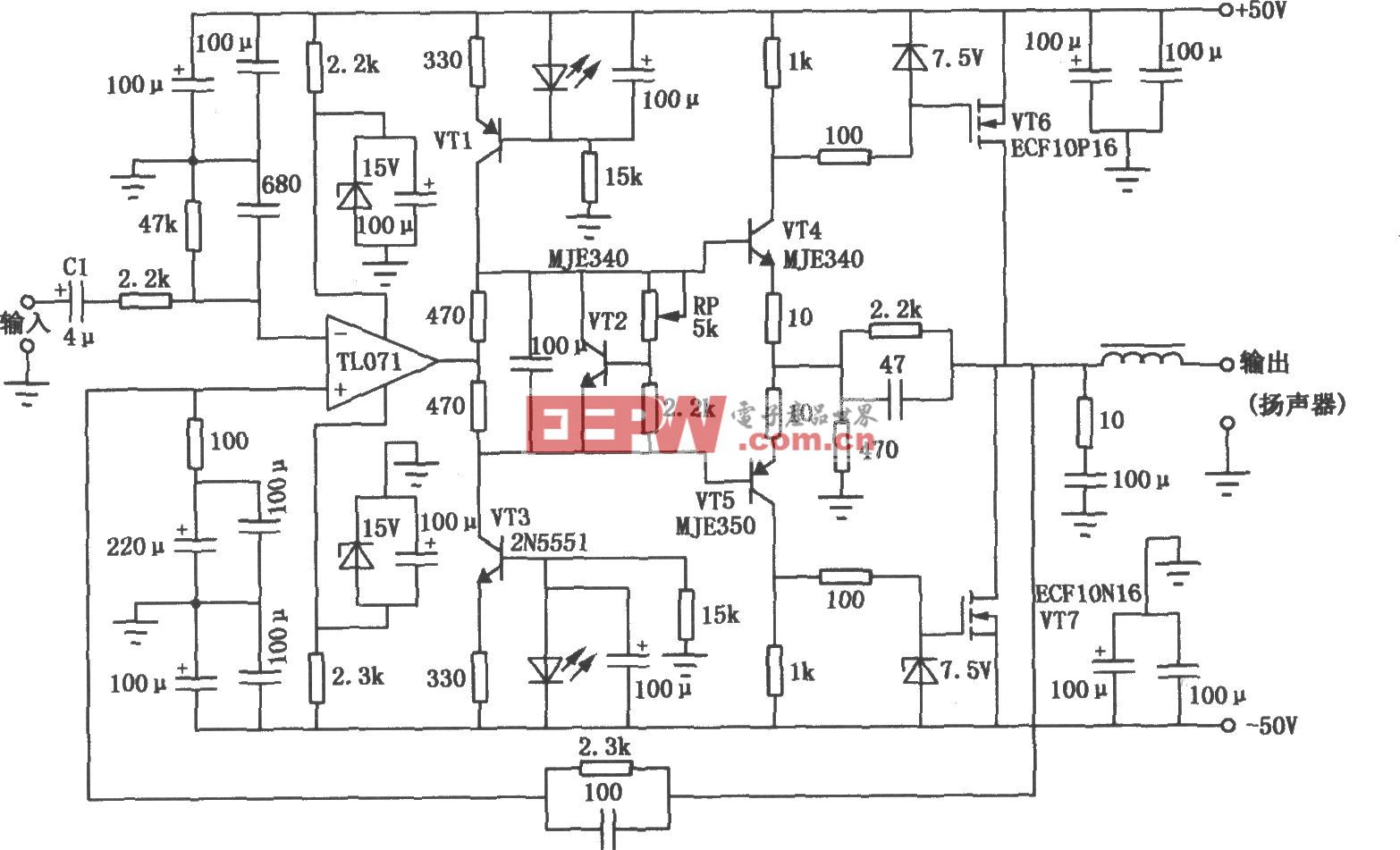

本电路主要由模/数转换器adc、输入电路、输出屯路、时钟电路和电源电路组成,如图2所示。

2.1.1时钟电路

2.1.1时钟电路

时钟电路的设计主要包括ad6644ast-65采样时钟相位噪声指标的确定以及pecl差分时钟的实现。

adc电路的孔径抖动有效值σ△tj,包括adc器件自

2.1.2 adc输入电路

adc输入电路多采用运放直流耦合或变压器交流耦合方式,为输入信号提供增益、偏置和缓冲。

由于运放为有源器件,除具有一定的谐波失真外,还存在主要集中在低频段的1/f噪声和较宽频带内的白噪声。这些噪声和谐波失真都降低了运放的信噪比snr和有效位数enob。当运放的snr不明显优于甚至低于adc的snr时,它带来的噪声是不容忽视的,对于高分辨率adc电路,甚至是不能接受的。而作为无源器件的变压器,一般认为它的噪声和谐波失真是微乎其微、可以忽略的。因此,本电路的输入电路采用变压器交流耦合方式,选用mini-circuits公司的变压器t4-6t。 为进行比较,同时也提供运放直流耦合方式,采用adi公司的低噪运放ad8138。根据ad8138的关参数,计算得到的ad8138输出的总谐波失真和热噪声之和大于1lsb。该指标可能导致无法满足电路热噪声不大于1.50lsb的设计要求,并带来更大的谐波失真。因此可预知,采用ad8138时,adc电路的有效位数enob会比采用变压器时的有效位数enob有所下降,甚至达不到设计要求。

2.1.3 adc输出电路

adc的模拟输入和数据输出之间存在少量的寄生电容,adc数据输出线上的噪声会通过这些寄生电容耦合到模拟输入端,导致adc的snr和有效位数enob下降。为解决这一问题,可在adc数据输出端接一锁存器。

为减小adc电源的波动,应尽量降低adc输出端的负载电容和输出电流。在adc数据输出端接一锁存器可避免将其直接连在数据总线上,有效限制了其输出端的负载电容;在adc每一个数据输出端都串联一个电阻,可限制其输出电流。

本电路采用74lc574作为ad6644ast-65的输出数据锁存器,同时每一个数据输出端都串联一个100ω的电阻。

2.1.4电源、地和去耦电路

ad6644ast-65的电源抑制比psrr≈±lmv/v,当外接电源的纹波为峰-峰值100mv时,等效于在ad6644ast-65输入端产生100μv(0.77lsb)大小的噪声,这相对于设计指标而言是不能接受的。为减小外接电源对电路的影响,本电路采用linear公司的低压差ldo线性稳压器ltl086-5和ltlll7-3.3(两个芯片的psrr均大于60db) 对外接稳压电源进行稳压,为ad6644ast-65等模拟电路提供5v电源和3.3v电源。

时钟、adc的输出信号以及后级数字电路的数字信号的跳变都会引起电源电流的急剧变化,由于印刷电路板的电源线和地线上存在分布电阻、电容和电感,当有变化的电流经过时,其上的压降也随之变化;频率较高时,就表现为电地间的高频杂波。为降低这类杂波干扰,本电路采取以下措施: · 时钟电路的5v电源,由vcc_5va串联一磁珠fb得到;

ad6644ast-65后级数字电路的3.3v电源,由vcc_3.3va串联一磁珠fb得到;

模拟地和数字地分开布线,并在一点用磁珠fb相连;

adc的所有电源管脚都就近对地接去耦电容。

磁珠对mhz级以上的信号有较好的吸收作用,能有效降低时钟电源、数字电源对ad6644ast-65模拟电源的影响,以及数字地对模拟地的影响。

去耦对于高速高分辨率adc电路尤为重要。为此,本电路采用0.01μf的npo材料(属低损耗、超稳定的电容材料,电气特性基本上不随温度、电压、时间的变化而变化,自谐振频率较高,适用于高频场合)自0 1206封装的贴片电容和0.1μf的x7r材料(属稳定性电容材料,电气特性随温度、电压、时间变化不明显,适用于中、低频场合)的0805封装的贴片电容并联,有效地滤除电地间较宽频带的杂波。

2.1.5电路板的布局布线

adc界于模拟电路和数字电路之间,且通常被划归为模拟电路。为减小数字电路的干扰,应将模拟电路和数字电路分开布局;为减小信号线上的分布电阻、电容和电感,应尽量缩短导线长度和增大导线之间的距离;为减小电源线和地线的阻抗,应尽量增大电源线和地线的宽度,或采用电源平面、地平面。本电路在设计印刷电路板时,都遵循了以上原则。 2.2电路测试结果

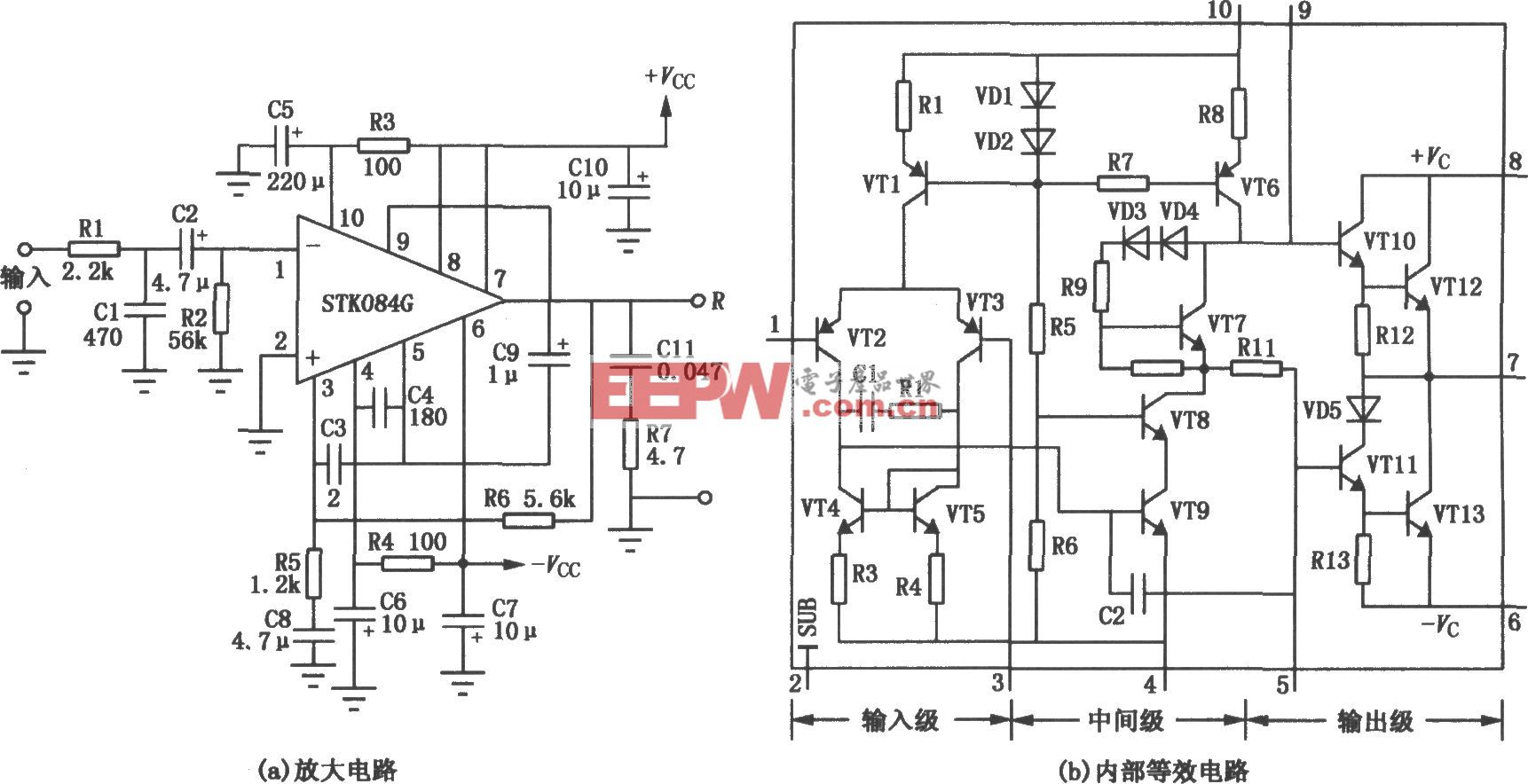

采用信号发生器hp8640b产生0~15mhz的单频正弦信号,经相应带通滤波器滤波(各次谐波均小于-90dbc)后作为本电路的输入信号,滤波后信号在ad6644ast-65输入端幅度为-ldbfs。

ad6644ast-65输出数字信号经74lc574锁存后,存储于逻辑分析仪hpl6702a中。hpl6702a状态分析时钟取自ad6644ast-65的dry管脚,该信号频率和ad6644ast-65采样时钟频率一致,为40mhz。

通过对逻辑分析仪hpl6702a每次存储的数字信号进行16384点fft分析,可得到奈奎斯特带宽内总功率pσ、输入信号功率只以及总谐波失真与噪声功率之和pn+thd=pσ-ps。经计算得到电路的有效位数enob=[sinad(db)-1.76]/6.02=[ps (db)-pn+thd (db)-1.76]/6.02。

图3(a)、(b)、(c)为在三种不同测试条件下,ad6644ast-65输出数字信号的fft分析频谱图和有效位数enob。

图3(c)表明,当fin=0.96mhz、ad6644ast-65输入端采用运放ad8138直流耦合时,电路热噪声和谐波失真明显增加,电路的有效位数enob约为10.74bit,比图3(a)的enob小0.6bit左右。由此可见,有源器件对高速高分辨率adc电路性能的影响是很大的。 理论分析和实际电路的测试结果都说明,高速高分辨率adc电路设计应选用低噪器件;当输入信号频率较高时,应选用低相位抖动的时钟源;在进行电路扳布局布线时,应注意电源噪声的抑制和减小数字电路对模拟电路的影响。

理论分析和实际电路的测试结果都说明,高速高分辨率adc电路设计应选用低噪器件;当输入信号频率较高时,应选用低相位抖动的时钟源;在进行电路扳布局布线时,应注意电源噪声的抑制和减小数字电路对模拟电路的影响。

评论