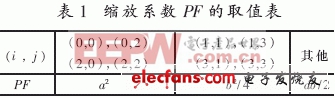

H.264_AVC视频编码变换量化核实现

2 4×4整数变换量化核的优化设计

为进一步提高硬件运算速度,减少硬件开销,设计中采用了如下优化方法:

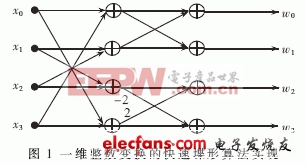

(1)在求取变换阵W=CXCT时,根据变换的对称性,将X的列变换(矩阵左乘)与行变换(矩阵右乘)分开实现,把二维变换分割为两次一维变换,并采用快速堞形算法[4]来实现。一维变换的快速算法实现如图1所示,其中的列变换可用如下算式表示:

对于每列变换,需要进行8次加法和2次移位运算,而行变换则可根据矩阵转置的性质ABT=(BAT)T,将经过列变换后的结果矩阵先进行转置,再采用相同的变换形式运算。这样对4×4点数据做一次变换,只需通过8×8次加法和2×8次移位运算便可完成。

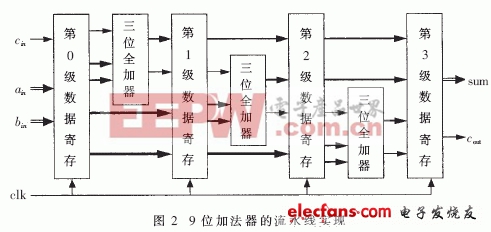

(2) 针对不同运算的位宽需要,设计专用的加法器和乘法器。本文对整数变换中的加法器采用三级流水线加法器,实现9位加法,每级流水线完成三位超前进位加法,将逻辑延迟限制在三位加法器之内。图2给出了9位加法器的流水线实现框图。选用EPF10K10LC84-3作为适配器件,经过Synplify Pro 7.3综合,结果表明这种加法器具有较优的最高工作频率和硬件开销。如表2所示, 常规加法器的最高工作频率为37.0MHz,消耗资源却为28LC,而经过优化的三级流水线加法器在消耗资源增加不多的情况下,其最高工作频率相比常规加法器提高了257%,达到94.5MHz。

评论