EMCCD图像传感器CCD97时序驱动电路的设计

电路的时间常数:

又因为上升时间与时间常数的关系为:

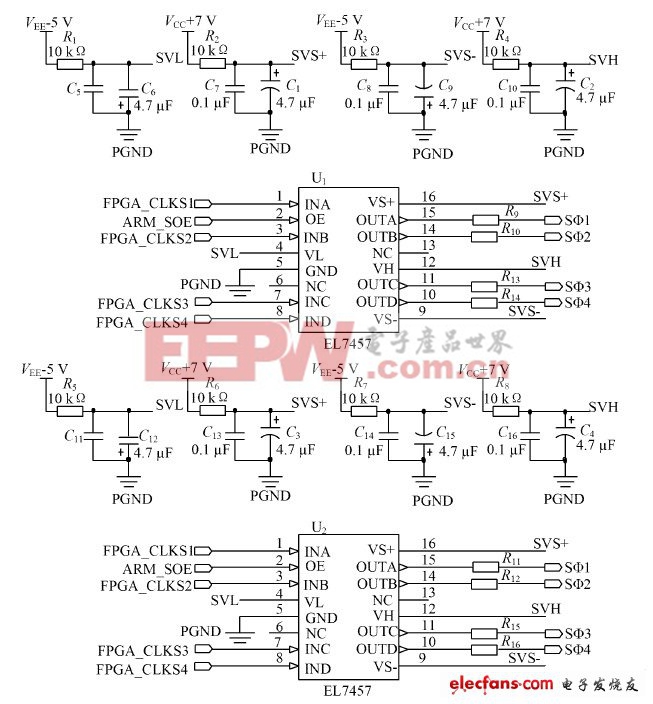

为了满足最佳上升时间( 200 ns) 的要求, 必须在EL7457 驱动输出端串上一个小电阻, 原理如图6 所示。

图6 中, FPGA _ CLKI1, FPGA _ CLKI2, FPGA _CLKI3, FPGA _ CLKI4 为FPGA 产生的T T L 时序。

ARM_IOE 为ARM 核产生的门控信号, 用来控制驱动脉冲I Φ1, 2, 3, 4 的开关。由于理论与实际计算的误差, 输出串接电阻R9 , R10 , R 13 , R14 将通过硬件调试过程确定, 以产生驱动CC97 工作的最佳波形。同理, FPGA_ CLKS1, FPGA _ CLKS2, FPGA _ CLKS3, FPGA _CLKS4 为FPGA 产生的TT L 时序。A RM _SOE 为ARM 产生的门控信号, 输出串接电阻待定。

图6 IΦ 1, 2, 3, 4; SΦ 1, 2, 3, 4 驱动产生

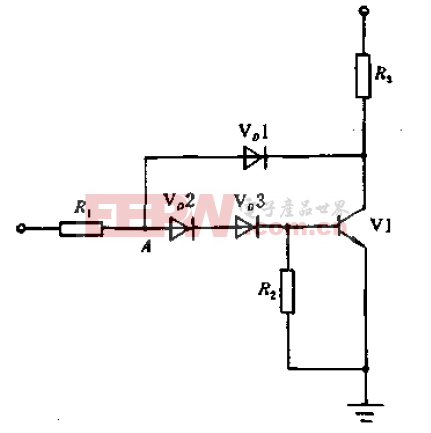

在RΦ1, 2, 3 产生电路中, 因为其电压摆幅要求为0~ 12 V, 故给它加以12 V 的电源( 见图7) 。

评论