13bit 40MS/s流水线ADC中的采样保持电路设计

3 采样开关的设计

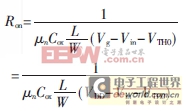

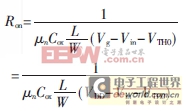

采样开关的性能在采样保持电路中占有十分重要的地位,对于一个简单的NMOS开关,开关导通时其导通电阻Ron为:

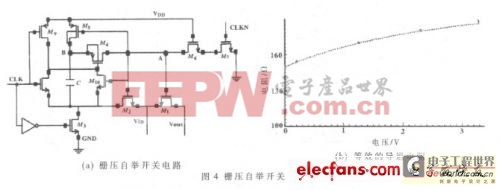

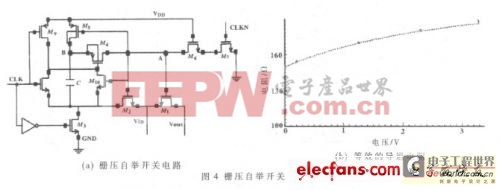

可见,导通Ron是一个与输入信号Vin相关的非线性电阻,这将在输出信号中引入谐波失真 [5]。本文采用如图4(a)所示的栅压自举开关,开关的导通电阻随输入信号幅值变化的曲线图如图4(b)所示,曲线的斜率大约为11 Ω/V,其导通电阻随输入信号幅值的变化较小,具有较高的线性度。

4 仿真结果

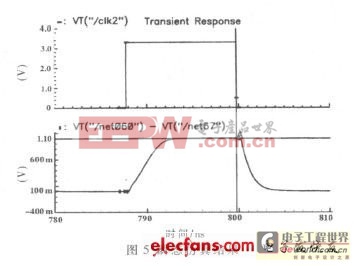

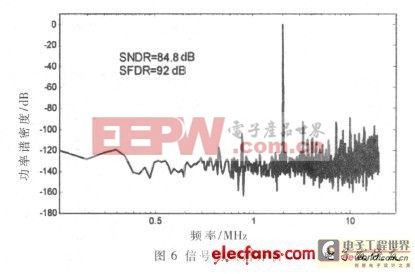

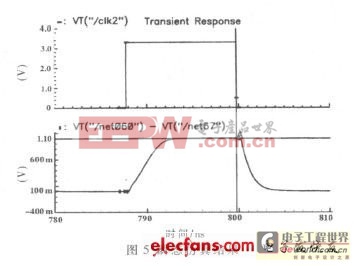

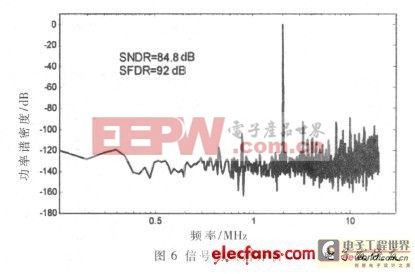

采用TSMC的0.18 μm工艺对电路进行了设计,电源电压为3.3 V,采样时钟为40 MHz,采用Spectre对电路进行了仿真。在采样保持电路的输入端加一值为1 V的阶跃信号,其瞬态仿真结果如图5所示。从图中分析得出,在保持相结束时刻,采样保持电路的输出幅值为1.000 08 V,与理想电压的误差为0.08 mV,建立精度达到了0.008%。图6所示为信号的频谱分析,输入峰-峰值为2 V,频率为1.992 187 5 MHz的正弦信号。对输出信号进行4 096点的FFT, 结果显示, 其SNDR为84.8 dB,SFDR为92 dB,有效位数为13.8 bit,能够胜任13 bit 40 MHz流水线型ADC对前端采样保持结构的要求。整个采样保持电路消耗的平均电流为8.501 mA。

评论