完整的HART兼容型4mA至20mA解决方案(一)

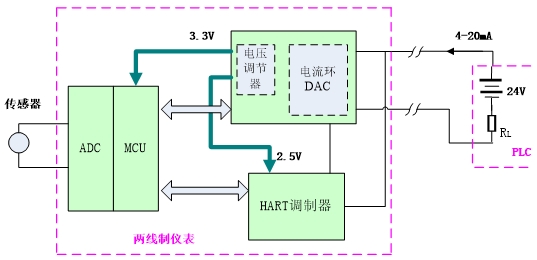

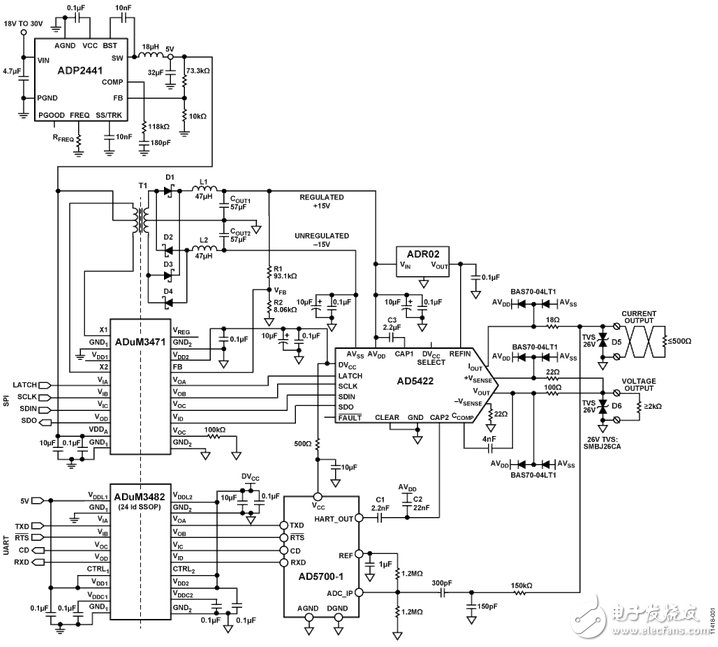

图3. AD5422和AD5700 HART调制解调器连接

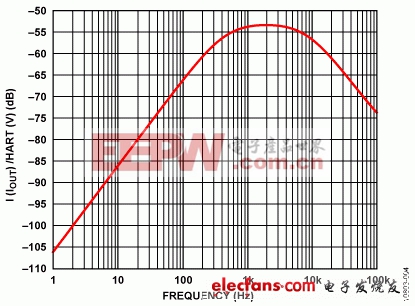

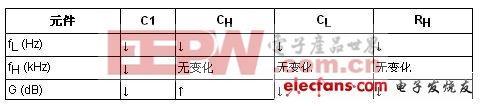

低通和高通滤波器电路通过RH、CL、CH和C1的相互作用并配合AD5422的一些内部电路来形成。在计算这些元件的值时,低通和高通频率截止点目标分别为》10 kHz和《500 Hz。图4显示了仿真频率响应的曲线图,表1显示了增加各元件而剩余元件值保持恒定对频率响应的影响。

图4. 仿真频率响应

表1. 个别元件值增加对频率响应的影响

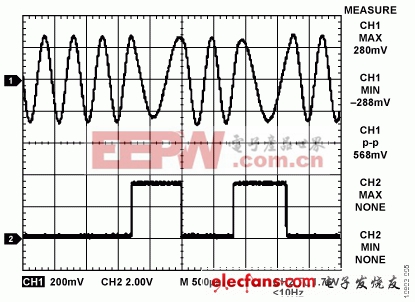

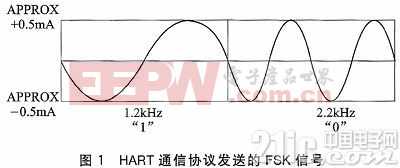

调制解调器的输出是一个FSK信号,包括1200 Hz和2200Hz移频。这个信号必须转换为1 mA峰峰值电流信号。为此,RSET引脚上的信号幅度必须衰减。这是因为AD5422采用内部电流增益配置设计。假定调制解调器的输出幅度为500 mVp-p,则其输出必须经过500/150 = 3.33倍衰减。此衰减通过RH和CL来实现。

本电路笔记中的测量使用以下元件值完成:

C1 = 4.7 nF

RH = 27 kΩ

CL = 4.7 nF

CH = 8.2 nF

图5表明在500Ω负载电阻上分别测得了1200 Hz和2200 Hz移频。通道1显示耦合至AD5422输出中的调制HART信号(设置为输出4 mA),通道2则显示AD5700 TXD信号。

图5. 在500Ω负载上测得的FSK波形

HART兼容性

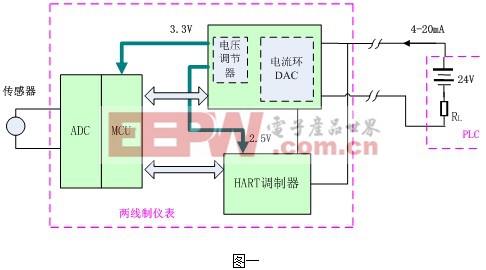

图1中的电路要与HART兼容,必须符合HART物范。HART规范文档中包含了众多物理层规范。其要的两个是静默期间输出噪声和模拟变化率。

静默期间输出噪声

当HART设备没有进行传输(静默)时,不应在HART扩展频带中将噪声耦合到网络上。噪声过高可能会干扰设备本身或网络上其它设备对HART信号的接收。

评论