面向安全硬件设计的新兴工具与技术

随着软件层面防御手段逐渐触及极限,行业注意力已转向直接在硅片中构建 “信任根”。本文剖析了可帮助设计人员自动化漏洞检测、保障供应链完整性的前沿技术。

设计安全硬件已不再是一门选修专业,而是任何现代片上系统(SoC)的核心要求。但识别并缓解硬件级漏洞,需要一套完善的专业工具生态与严格的架构设计原则。

硅基信任根

本文深入介绍当今硬件工程师可使用的实用技术工具集。我们将分析关键工具与架构技术,例如硬件安全区、形式化验证等,帮助工程师在芯片内部保护知识产权与敏感数据。

安全架构技术

硬件信任根(HRoT) 是系统最基础、不可篡改的信任来源。它直接在硅片中实现 —— 通过安全启动 ROM 或专用安全控制器 —— 执行数字签名验证、加密密钥管理等关键功能。其核心目标是确保从上电那一刻起,只有未经篡改的正版代码得以运行,从而建立可靠的信任链。

可信执行环境(TEE) 在处理器内部创建安全隔离区,与主操作系统(富操作系统)进行逻辑与物理隔离。通过硬件资源隔离,即使主操作系统内核被攻破,TEE 仍可保护敏感数据与关键算法的执行。

Arm TrustZone、Intel SGX 等行业标准均采用此类架构,在受保护环境中处理生物识别数据与安全支付业务。

侧信道攻击防护 旨在阻断通过硬件物理信号意外泄露信息的风险。设计人员会部署专用逻辑,防止攻击者通过分析芯片运行时的功耗、电磁辐射或时序差异推导出加密密钥。

核心技术包括:常量时间编程、功耗负载均衡,以及在关键操作中加入随机噪声或抖动。

设计工具与框架

Caliptra 是一款开源信任根规范,可作为可复用 IP 模块集成到 SoC 中。其标准化架构支持安全启动与透明硬件身份标识,解决了专有方案不透明的问题。

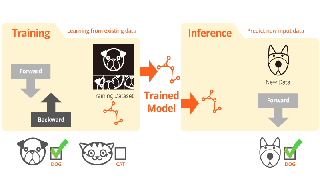

形式化验证工具 采用严谨的数学方法,证明芯片设计严格符合其安全规范。与传统仿真测试不同,形式化验证会分析系统所有可能状态,在芯片流片前识别侧信道攻击、信息泄露等关键漏洞。

安全 CAD 工具 是新一代计算机辅助设计工具,将安全防护指标融入标准开发流程。这些工具可帮助工程师自动插入防护措施,如逻辑混淆、硬件木马检测等,让安全设计与功耗、性能指标同等重要。

新兴趋势

随着量子计算发展,传统加密算法面临安全风险。后量子密码(PQC) 的硬件实现重点在于集成可执行抗量子算法(如格基密码)的加密加速器。设计人员面临的挑战是,在不牺牲能效与芯片面积的前提下集成这些功能,确保现有设备在后量子时代依然安全。

供应链安全 旨在保障硬件从制造到最终交付的完整性。针对芯片翻新、假冒、制造过程中植入硬件木马等威胁,行业正部署物理不可克隆函数(PUF)、区块链追踪等技术。这些工具为每颗芯片生成唯一 “数字指纹”,确保硬件为正品且未被恶意篡改。

专用硬件模块设计约束与实现挑战

尽管这些安全技术在理论上十分可靠,电子工程师在实现阶段仍需权衡诸多关键因素:

部署硬件信任根与基于 TEE 的隔离需要占用专用硅片面积,直接影响设计的 PPA 指标(功耗、性能、面积)。集成这些功能会增加总门数与功耗,对电池供电的物联网设备或面积受限的专用集成电路(ASIC)而言可能难以接受 —— 每平方毫米硅片都极为宝贵。

芯片安全防护会使验证范围呈指数级扩大。标准 EDA 工具通常仅针对功能正确性优化,并不擅长检测细微的信息泄露。工程师必须使用专用形式化验证与侧信道分析工具,这可能显著延长产品上市时间。

迈向安全优先的硬件设计

从软件定义安全转向硅基信任,已不再是战略选择,而是技术刚需。

集成硬件信任根、可信执行环境等架构,同时合理平衡 PPA 代价,是在后量子时代保护全球供应链与敏感数据的唯一可行路径。

对现代电子工程师而言,核心挑战在于熟练掌握新一代 EDA 与形式化验证工具,确保安全能力在寄存器传输级(RTL)设计阶段就深度融入,而非事后补救。

最终,只有构建统一、强健的硬件级防御体系,才能为真正高韧性的数字生态筑牢根基。

评论