USB差分信号线PCB布线指南

本文介绍了在PCB上正确布局USB差分数据线的关键原则和实践。主要目标是实现USB 规范中规定的90欧姆阻抗匹配。且应考虑ESD 保护及完整的地平面。

1 USB速度等级及阻抗要求

USB的速度标准经历了多次迭代,不同版本的USB接口速度差异很大。以下是常见USB标准的理论最大传输速度:

USB版本最大传输速度(理论值)常见名称备注

对于USB 1.1、USB 2.0, 理论最大速度不超过480M,因此虽然也需要满足基本的差分对走线约束以及90欧阻抗匹配的要求,但对Layout 的要求并不高,满足通用约束基本都能使用。但对于USB 3.0 以上的版本,速率从480 Mbps 跃升到5 Gbps,其布局布线的要求要严苛得多,因为高速信号线对PCB 上的任何物理瑕疵都极为敏感。

2 通用USB布线约束

首先要记住核心原则:一切为了90 欧姆阻抗决定差分阻抗的主要物理参数有四个:

2.1 走线宽度:线越宽,阻抗越低。

2.2 走线间隙:两条线间隙越近,耦合越强,差分阻抗越低。

2.3 介质厚度(PP):走线距离其下方参考平面(通常是GND 层)的高度。距离越远,阻抗越高。

2.4 介质常数(Er):PCB 板材的特性。最常用的FR-4 材料,Er 值通常在4.2 到4.6 之间。

因此,要回答“走线多宽,间距多大?”,必须先确定您的PCB 层叠结构,然后使用阻抗计算工具(如Polar Si9000、Saturn PCB Toolkit、华秋DFM 或EDA 软件自带的计算器)来反向计算出合适的宽度和间隙。

3 常见场景下的参考值

尽管没有固定值,但在业界最常见的4 层板、FR-4板材、标准叠层设计中,确实有一些被广泛使用的“经验值”或“起始值”。您可以将这些值作为您设计的起点,然后根据您的实际板厂参数进行微调。

以下是一些典型场景的参考值(目标:90 Ω 差分阻抗):

场景一:最常见的4 层板(信号- 地- 电源- 信号)

层叠:顶层(信号)到第二层(地)的介质厚度通常在6-8 mil(0.15-0.20 mm)之间。

铜厚:0.5 oz(17.5 um)或1 oz(35 um)。

常见组合1:

线宽:5 mil(约0.127 mm)

间距:7 mil(约0.178 mm)

常见组合2:

线宽:6 mil(约0.152 mm)

间距:6 mil(约0.152 mm)

场景二:介质层较厚的情况

如果信号层到参考地层的距离较厚, 比如10-12 mil,为了维持90 Ω 阻抗,走线需要做得更宽。

可能组合:

线宽(Width):7 mil(约0.178 mm)

间距(Spacing):6 mil(约0.152 mm)

4 最佳实践与建议

以上只是理论计算,实际操作时,最重要的步骤是与板厂沟通,向板厂索要他们推荐的层叠结构,这样才能获取各层厚度、介质尝试等信息,用于阻抗的精确计算。

这里推荐一个省事儿的方法,使用华秋DFM里的阻抗计算工具。由于华秋本来也是板厂,所以DFM工具里可以直接获取到他们家常用的层叠信息,不用再费力地与厂家电话沟通或者去网站上搬运参数。具体使用步骤如下:

1.打开华秋DFM的阻抗计算工具:

2.设置层数、板厚、内外层铜箔厚度,然后选择玻璃布的型号。这一步很重要,玻璃布的型号决定了很多计算阻抗的关键参数。

以下是常用的玻璃布型号。

玻璃布型号标称原始厚度压合后厚度典型Dk@1GHz一句话记忆:

在DFM中算阻抗最大的优点在于这些层叠结构和实际制造PCB时选用的层叠完全一致,不存在沟通上的问题。同时,选取型号后,参数会自动展示在阻抗计算器中,无需手动填写:

3.输入目标阻抗90欧,假设走线间距设为7 mil,点击“反算”,即可得出差分对的走线宽度:

结果会自动填充到上方的阻抗列表,方便进行再次验证:

5 地平面的要求

无论是微带线还是带状线,都要求USB差分对有完整(不能夸平面)的参考平面,以提供最短的回流路径。尤其是USB 3.0以上的版本,这点至关重要。

KiCad中进行USB设计

在原理图设计时,必须使用_P/_N或+/- 后缀定义差分对信号:

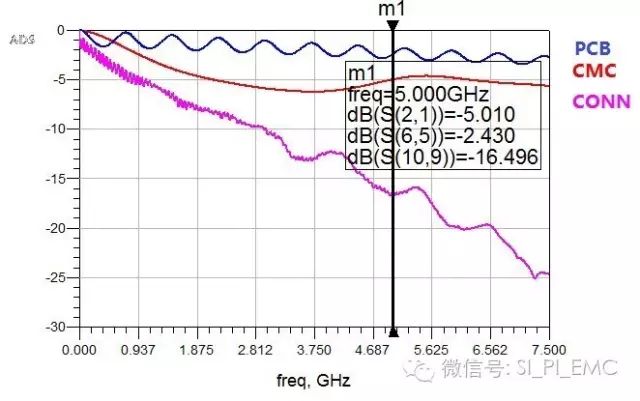

由于USB接口是暴露在系统外的,且经常拔插。因此强烈建议增加ESD保护芯片,防止因为静电等意外情况击穿相对较贵的主芯片(如主控CPU、USB控制器、电源管理IC等)。任何与外界直接相连的接口,都必须考虑静电放电(ESD)和电磁干扰(EMI)的防护。在靠近USB连接器的数据线和电源线上,应合理布局ESD保护器件(如TVS 二极管)和共模电感(Common Mode Choke)。ESD器件能够瞬间钳位有害的静电电压,保护后级电路;而共模电感则能有效抑制差分线上的共模噪声,进一步提升信号的抗干扰能力。这些防护器件的布局原则是尽可能靠近连接器,在有害能量进入主板深处之前就将其吸收或滤除。

在做PCB Layout时,需要注意以下几点:

1.如果差分对在顶层或底层(微带线),下方必须有完整的参考地平面,不允许出现信号跨越平面的情况。

2.使用自定义的DRC 规则,限制差分对的线宽、间距以及最大非耦合长度。

我们还可以使用通配符或正则表达式定义一个差分对的网络类:

然后使用“自定义规则”为DP的差分对网络类定义特殊的规则。比如下图定义了差分对间隙为

6 USB 3.0的额外要求

对于USB 3.0,需要将这些原则执行得更加极致,并关注以下几个特殊且关键的要求:

1.严格的阻抗控制:不止是D+/D-

USB 3.0 引入了全新的SuperSpeed差分对:一对用于发送(SSTX+/SSTX-),一对用于接收(SSRX+/SSRX-)。这两对线路与原有的USB 2.0 的D+/D- 线路是独立的。

目标阻抗:所有SuperSpeed差分对(SSTX和SSRX)都必须严格控制90 Ω±7% 的差分阻抗。相比USB 2.0 的90 Ω±15%,这个容差要求严格了1倍。这意味着您需要通过PCB叠层设计和阻抗计算工具,精确确定走线的宽度、间距和参考平面距离。

D+/D-线路:同时,板上的D+/D-线路仍需保持90欧姆的差分阻抗,以兼容USB 2.0模式。

2.极致的差分对内等长控制

在5 Gbps的速率下,信号传播时间的微小差异都会导致数据采样错误。

对内等长:SSTX+与SSTX-之间的长度差异,以及SSRX+与SSRX-之间的长度差异,必须控制在极小的范围内。业界通常建议不超过5mil(0.127毫米)。

这通常需要通过在较短的走线上添加蛇形线来进行精确补偿。

请注意,SSTX 差分对与SSRX 差分对之间不需要做等长匹配。

3.明确的隔离与间距要求

高速信号非常容易受到外部噪声的干扰,也容易对外产生干扰。

远离噪声源:SuperSpeed 差分对应远离晶振、时钟线、开关电源(SMPS)以及其他周期性信号线路。一个常用的经验法则是“3 W 原则”,即高速线与其他信号线的间距应至少是线宽的三倍。

差分对间距:为防止串扰,SSTX 与SSRX 差分对之间,以及它们与D+/D- 差分对之间,都应保持足够的距离,建议至少保持20 mil(0.5 毫米)以上的间距。

4.完整的参考平面与最短的回流路径

这是所有高速设计的基础,但在USB 3.0 中尤为重要。

连续的参考平面:SuperSpeed差分对的走线下方必须是完整且连续的地平面(GND Plane)。绝对不允许跨越地平面分割区域。信号的回流路径会沿着走线正下方的地平面返回源端,任何中断都会极大破坏阻抗连续性,形成天线效应。

多层板是标配:强烈建议使用至少四层板(信号层- 地层- 电源层- 信号层)。这样可以为高速信号提供一个理想的、低阻抗的参考平面。

5.最小化并优化过孔(Via)的使用

过孔是高速信号路径上的“天坑”。

尽量避免:在SuperSpeed 差分对的路径上应尽一切可能避免使用过孔。过孔会引入寄生电容和电感,是严重的阻抗不连续点。

必须使用时:如果实在无法避免,必须成对、对称地使用过孔,并在过孔旁放置“接地过孔”(Stitching Via),以确保信号回流路径的连续性。

USB 2.0 vs USB 3.0布线关键差异

简而言之,USB 3.0的布局布线不再是简单的“把线连上”,而是需要运用射频和微波领域的信号完整性知识。每一个转角、每一个过孔、每一毫米的长度差异,都可能成为影响最终性能的决定性因素。

7 结束语

成功的USB PCB 布线,并非依赖于某种神秘的直觉,而是建立在对信号完整性、阻抗控制和电磁兼容性深刻理解之上的严谨工程实践。从守护核心的差分对开始,为其提供完整的参考平面,保证电源的纯净,并构筑起牢固的防护壁垒,每一个环节都至关重要。遵循这些最佳实践,您的设计将不再“随缘”,每一次的连接都将是稳定与高效的保证。

(本文来源于《EEPW》202510)

评论