攻克28G PAM4抖动难题!差分输出VCXO如何重塑光通信时钟架构

差分输出VCXO定义与技术价值

本文引用地址:https://www.eepw.com.cn/article/202506/471854.htm在400G/800G光模块的56Gbaud PAM4调制系统中,时钟抖动每增加0.1ps RMS,误码率将飙升300%。传统单端CMOS时钟源因共模噪声干扰,难以满足高速SerDes对相位稳定性的严苛需求。差分输出VCXO(压控晶体振荡器)通过对称差分信号(LVDS/HCSL) 实现共模噪声抑制,结合±50ppm频率微调能力,将相位抖动压缩至0.7ps RMS以下,成为高速光通信系统的“精密心跳发生器”。

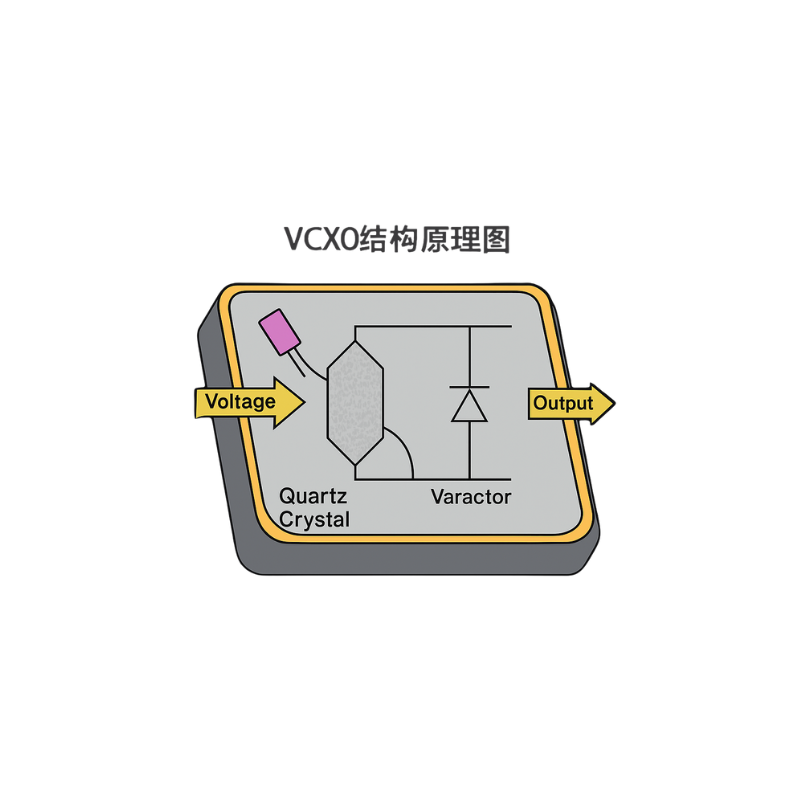

VCXO结果原理图

差分架构的工程突破

1. 抗噪革命性设计

● 双线抵消机制:差分对(D+/D-)输出幅度相等、极性相反,可抵消90%以上电源/地线噪声

● 阻抗匹配优化:100Ω差分阻抗精准匹配传输线,减少信号反射造成的相位畸变

● 抖动传递函数:较单端输出降低相位噪声20dBc/Hz@100kHz偏移(实测数据)

2. 超低抖动核心技术

注:基于156.25MHz频点测试数据,满足IEEE 802.3ck标准

光通信系统的三大关键应用

1. 400G光模块时钟树架构

在QSFP-DD封装中,差分VCXO直接驱动DSP芯片:

● 频率牵引范围:±50ppm(±0.8V调谐电压)补偿温度漂移

● 启动稳定性:5ms内锁定目标频率,加速模块初始化

● 典型配置:156.25MHz LVDS输出,相位噪声-150dBc/Hz@1MHz

2. 高速ADC/DAC采样时钟

在相干光通信系统中:

● 驱动64Gsa/s ADC时,INL(积分非线性度)改善40%

● 配合锁相环实现fs级抖动传递,提升EVM(误差矢量幅度)3dB

3. PHY层芯片参考时钟

为56G PAM4 SerDes提供时钟:

● 消除传输线串扰导致的确定性抖动

● 支持-40℃~+85℃全温域频偏<±2ppm

主流方案参数横评

表:光通信差分VCXO关键指标对比

技术趋势解析:

● SiTime MEMS方案:凭借半导体工艺将温漂压缩至±0.1ppm/℃

● NDK超低抖动技术:采用SC切割晶体,近载波相位噪声优于-130dBc/Hz@100Hz

● Rakon抗振设计:振动灵敏度<0.1ppb/g,适应基站恶劣环境

封装与电源兼容性创新

1. 微型化封装革命

● 3225(3.2×2.5mm)表面贴装:较传统7050封装体积缩小70%

● 金属屏蔽腔体:隔离外部EMI干扰,屏蔽效能>60dB

● 底部导热焊盘:热阻降至15℃/W,温升降低40%

2. 电源适应性突破

● 宽电压输入:2.5V/3.3V双模式兼容

● PSRR优化:80dB@100kHz电源纹波抑制比

● 智能启动电路:抑制上电浪涌,避免时钟毛刺

设计选型黄金法则

1. 抖动预算分配:系统总抖动中VCXO贡献需<15%(56G PAM4系统要求<1ps)

2. 频点匹配策略:

● 100G/400G光模块:155.52MHz/156.25MHz

● 5G前传:122.88MHz/245.76MHz

● 数据中心互连:322.265MHz

3. 可靠性验证要点:

● 10年老化率<±3ppm

● 2000次热冲击(-55℃↔+125℃)频偏<±0.5ppm

结语:精密同步时代的核心引擎

差分输出VCXO以0.7ps RMS超低抖动和±50ppm精准调谐能力,正成为800G光模块、56G SerDes及毫米波系统的同步基石。随着硅基MEMS工艺突破,新一代VCXO将在1.6T光通信时代实现0.3ps抖动极限,配合多通道输出版本(如4路差分时钟),为CPO(共封装光学)架构提供全系统同步解决方案。当光通信进入800G/1.6T时代,这颗不足5mm²的“时钟心脏”将成为决定系统性能的胜负手。

评论