PCIe 7.0规范发布,翻倍狂飙128GT/s

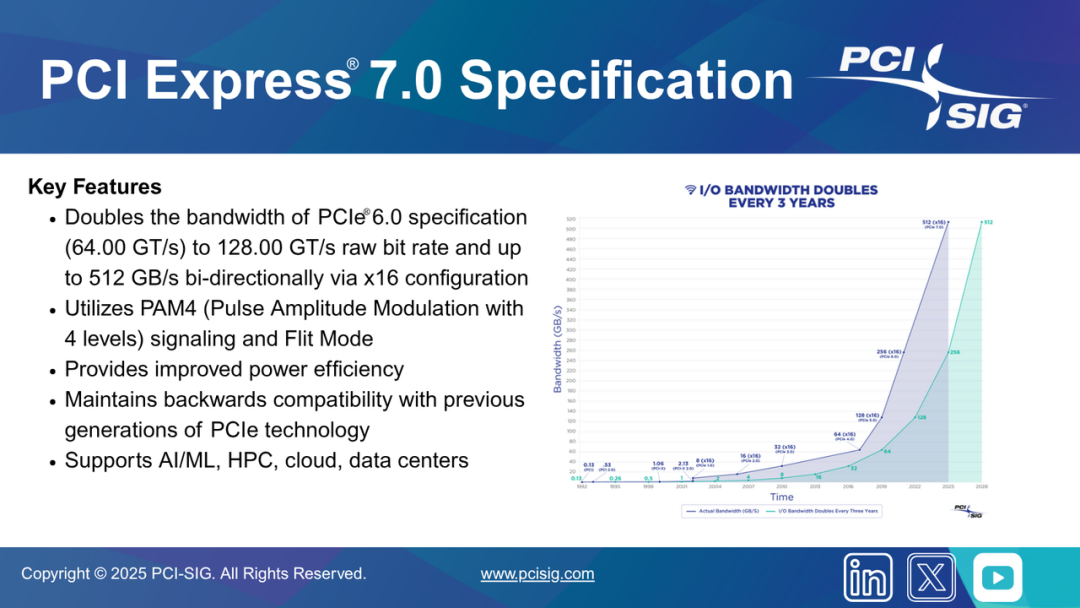

PCI-SIG 正式发布了 PCIe 7.0 规范。这是继 PCIe 6.0 发布三年多以来的一次重要更新,新一代标准再次实现了传输带宽的翻倍提升。

本文引用地址:https://www.eepw.com.cn/article/202506/471381.htm

PCIe 7.0 的原始比特率达到了 128.0 GT/s,在常用的 ×16 配置下,实际数据传输速度最高可达双向每秒 512GB。这意味着,即便是在 ×4 的配置下,PCIe 7.0 的带宽水平也可媲美上一代 PCIe 5.0 在 ×16 下的表现。

和 PCIe 6.0 一样,PCIe 7.0 同样采用了 PAM4 信号编码方式,并进一步优化了能效表现。新的规范在提升性能的同时也保持了与此前各代 PCIe 技术的兼容性。目前,下一代 PCIe 8.0 的规划工作也已同步展开。

PCI-SIG 主席兼首席执行官 Al Yanes 表示:「在过去二十多年中,PCIe 技术一直是高性能、低延迟 I/O 连接的首选解决方案。我们很高兴宣布 PCIe 7.0 规范正式面世,这延续了我们一直以来每三年将 I/O 带宽提升一倍的发展节奏。」

他同时指出,随着人工智能应用的快速演进,对数据传输能力的需求持续增长。新一代 PCIe 技术能够有效支持如超大规模数据中心、高性能计算、汽车电子以及航空航天等高带宽需求领域的未来发展。

More Than Moore 首席分析师兼首席执行官 Ian Cutress 表示:「PCIe 规范的最终版本发布是一个特殊的时刻,尽管业界围绕高速信号制定标准非常复杂,但通过 PCIe 技术实现的计算和网络需求的增长却达到了前所未有的水平。数据中心已准备好开始部署基于 PCIe 7.0 技术的网络,而且几乎我接触到的每一家 ASIC 公司都已与 IP 提供商接洽,并准备从中获益。尽管 PCIe 6.0 的部署已经非常流行且备受关注,但 PCIe 7.0 规范比以往任何版本都更受关注。」

PCIe 7.0 标准将于 2027 年完成预发布测试 (Pre-FYI),初始集成商名单预计将于 2028 年发布。

光学感知重定时器 ECN

除了发布规范之外,PCI-SIG 还宣布了新的光纤互连规范修订,以实现更高的 PCI Express (PCIe) 技术性能。「光学感知重定时器工程变更通知 (ECN)」修订了 PCIe 6.4 规范和新的 PCIe 7.0 规范,纳入了基于 PCIe 重定时器的解决方案,从而提供了首个通过光纤实现 PCIe 技术的行业标准化方法。

PCI-SIG 总裁兼主席 Al Yanes 表示:「我们看到了基于 PCIe 技术的行业标准光互连的需求,而 Optical Aware Retimer ECN 是添加模块化光解决方案的第一步。我们预计该技术将首先应用于人工智能/机器学习和云等数据中心应用。随着 PCIe 技术逐渐普及,我们预见到众多细分市场将出现创新用例。」

光学感知重定时器 ECN

无缝支持各种光学技术,用于现有符合 PCIe 6.4 和 7.0 规范的交换机、根复合体和端点硅片设计之间的光学互连

扩大机架和舱室的覆盖范围

允许跨电域和光域进行多路复用和数据映射

比铜缆解决方案更紧凑的实现

PCIe 标准发展历程

自 2003 年推出以来,PCIe 发展至今已经从最初的 1.0 升级到了 7.0,下面我们来简单了解下 PCIe 标准的演进历史以及各代 PCIe 标准之间的主要差异

最早第一代 PCIe 1.0 标准于 2003 年推出,支持每通道 2.5GT/S 的传输速率和每通道 250MB/S 的数据速率。

2007 年初,第二代 PCIe 推出,每通道传输速度为 5 GT/s,吞吐量(带宽)也增加了一倍,达到每通道 500MB/s,但由于 8b/10b 编码方案的开销占比为 20%,因此单 lane 的传输带宽为 4 Gb/s。

PCIe 3.0 及以后的版本使用更高效的 128b/130b 编码,将开销占比降低到了 1.5%。通过减少开销占比,PCIe3.0 的单 lane 传输带宽相比 PCIe2.0 翻倍,达到 8 Gb/s,同时保持了与 PCle 2.0 版本软件和机械接口的兼容性。PCIe 3.0 规范包含了 Base 和 CEM(卡机电)规范,其中基本规范里的电气部分定义了集成电路级的电气性能,并支持 8 GT/s 信令。

PCIe 4.0 标准是在 2017 年推出。与前一代相比,PCIe 4.0 将传输速率从 8 Gb/s 提高至 16 Gb/s,并与前几代技术从软件到时钟架构再到机械接口充分兼容。PCIe 4.0 在规范中增加了计时器部分以扩展通道的范围,并特别增加了系统的复杂性测试。

2019 年 5 月推出了 PCIe 5.0 规范,将传输速率提高一倍,达到 32 GT/s,同时保持低功耗和与前几代的向后兼容性。PCIe 5.0 承诺通过 x16 配置达到 128 GB/s 的吞吐量,在数据中心可实现 400GE 的速度。PCIe 5.0 和 400GE 的速度共同支持人工智能(AI)、机器学习、游戏、视觉计算、存储和网络等应用。PCIe 5.0 使用 128b/130b 编码方案,该方案在 PCIe 3.0 和兼容的 CEM 连接器中首次亮相。

2022 年 1 月推出了 PCIe 6.0 规范,它是第一个使用脉冲幅度调制 4 级(PAM4)信号编码的 PCI Express 标准,使 PCIe 6.0 设备在保持相同信道带宽的情况下能实现 PCIe 5.0 设备两倍的吞吐量。PCIe 6.0 技术最高可达 64 GT/s,同时保持低功耗和向后兼容。PCIe 6.0 承诺通过 x16 配置达到 256GB/s 的吞吐量,在数据中心实现 800GE 速度。

评论