使用两点校准消除ADC偏移和增益误差使用两点校准消除ADC偏移和增益误差

通过示例了解两点校准方法和定点实现,以补偿模数转换器(ADC)偏移和增益误差。

在上一篇文章中,我们讨论了单点校准可用于微调ADC偏移误差。为了补偿偏移和增益误差,我们需要两点校准。在本文中,我们将探索两点校准方法,并通过一个例子了解该技术的定点实现。

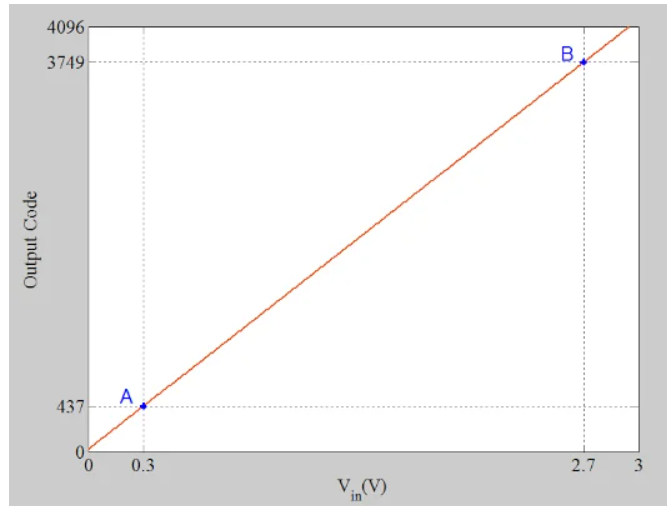

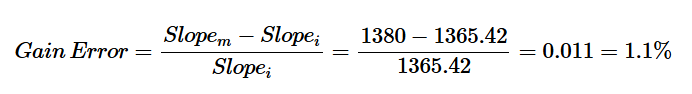

图1显示了受偏移和增益误差影响的单极12位ADC的特性曲线。

受偏移和增益误差影响的单极12位ADC的特性曲线。

图1。受偏移和增益误差影响的单极12位ADC的特性曲线。

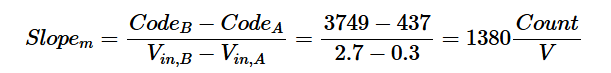

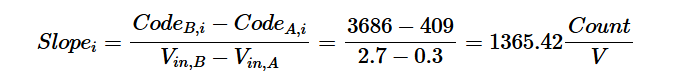

ADC的满标度值为3V。选择ADC满标度范围10%和90%的两个测试输入点A和B,以确定ADC偏移和增益误差。在0.3V和2.7V时,测量的输出代码分别为437和3749。测量的传递函数的斜率可以计算为:

使用点A的x和y值,我们得到以下直线方程:

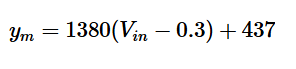

通过替换Vin=0,发现偏移误差为+23 LSB。以下方程式描述了理想12位ADC的线性模型:

因此,0.3V和2.7V下的理想码值分别为409和3686。使用这些值,理想响应的斜率可得:

现在我们可以计算ADC的增益误差如下:

两点校准——消除ADC偏移误差和增益误差

知道实际响应后,我们现在可以很容易地消除数字域中的偏移和增益误差。首先,我们可以从每个输出代码中减去偏移量,得到一个通过原点且斜率为Slopem的响应。接下来,将结果乘以

SlopeiSlopem

将获得的直线绕原点旋转,并产生斜率为Slopei的直线。

这些数学运算将实际响应的直线映射到理想ADC的直线。图2使用了一个夸张的例子来说明校准概念。

显示ADC校准的示例响应。

图2:显示ADC校准的示例响应。

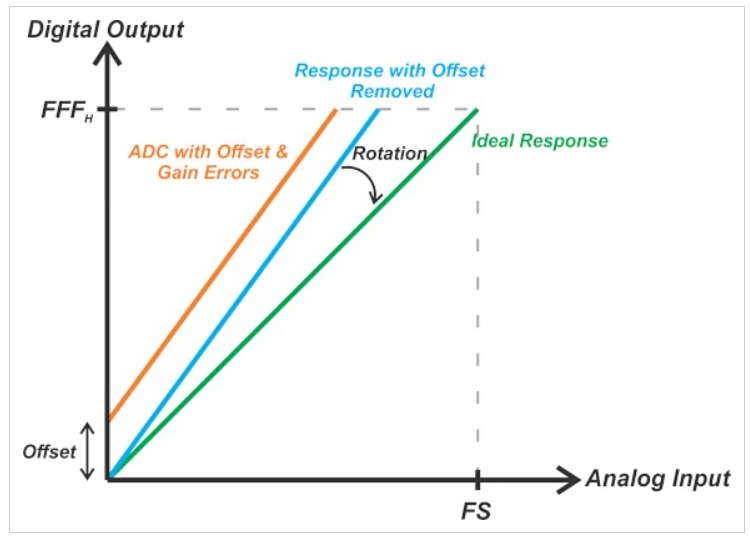

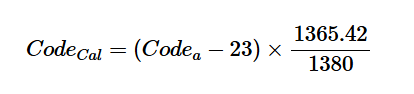

因此,通过应用方程式1,可以从实际代码Codea计算出校准的输出代码CodeCal:

方程式1。

定点校准实施

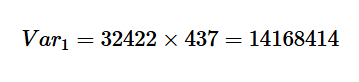

另一方面,如果我们试图补偿偏移和增益误差的固定值,我们可以简化方程1,实现计算效率更高的系统。继续我们的例子,我们可以将offset=23、Slopei=1365.42和Slopem=1380代入方程1,得到以下关系:

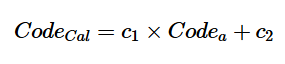

为了节省系统处理器的一些CPU(中央处理单元)周期,我们可以将上述方程简化为方程2:

方程式2。

解释:

c1=0.989434782

c2=-22.757

虽然我们可以使用浮点算法来实现上述方程,但定点实现可能更高效、更划算。我们有两个分数,c1和c2。为了以定点格式表示分数,我们将使用隐含的二进制点。这意味着我们将假设寄存器的一定数量的位表示整数部分,而剩余的位表示数字的小数部分。

然后使用Q格式表示法来指定整数和小数部分的位数。例如,101.0011可以是Q3.4格式的数字,因为它使用三位表示整数,四位表示小数部分。

请注意,二进制点实际上并没有在硬件中实现;它只是一个概念,允许我们在定点处理器中表示分数。此外,给定Q格式的数字可能表示正值或负值。

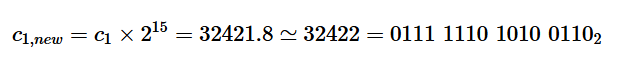

回到我们的ADC校准示例,我们有两个分数c1和c2,它们应该以适当的定点格式表示。让我们假设使用二进制补码格式的带符号16位寄存器来存储这些常数。由于c1小于1,整数部分只需要一个比特作为符号。其余的比特可以表示小数部分,从而形成Q1.15格式。

为了找到c1的不动点表示,我们将其乘以215,将其四舍五入到最接近的整数,并将舍入结果转换为二进制形式。

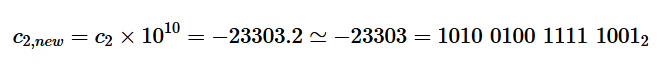

由于c2在16到32之间,我们需要5位用于整数部分,1位用于符号。这给我们留下了10位用于小数部分。因此,c2的适当表示是Q6.10格式。为了用这种格式表示,我们将c2乘以210,将其四舍五入到最接近的整数,并将四舍五进的结果转换为二进制形式。

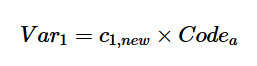

请注意,c2是2补码格式的负数。由于新系数使用不同的缩放因子,我们需要仔细跟踪缩放因子对计算的影响。让我们定义一个新的临时变量Var1,将c1、new和未校准ADC读数的乘积存储为方程式3:

方程式3。

这产生了方程2右侧的第一项。假设ADC的12位输出存储在C程序中的带符号16位寄存器中。因此,Codea可以被视为Q16.0数字。这意味着实现方程式3需要将Q1.15值乘以Q16.0值。变量Var1应该是一个32位寄存器来存储此乘法的结果。此外,由于Q16.0的数字乘以Q1.15的值,Var1的格式为Q17.15。如果你需要使用定点表示法来复习乘法,请参阅这篇文章。

如您所见,乘法运算增加了数据字长。在实现DSP(数字信号处理器)算法时,我们通常会截断或舍入乘法输出,以防止字长无限增长。然而,在截断或舍入乘法输出之前,我们应该考虑对数据的下一步操作。

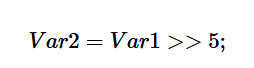

在这个例子中(方程式2),乘法结果将被添加到Q6.10格式的c2 new中。考虑到c2的分数部分,我们可以丢弃Var1的五个最低有效位,并将截断的结果存储在一个新的变量Var2中。C编程中的右移运算符可用于执行此操作:

方程式4。

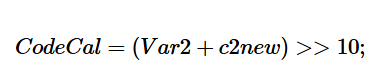

如果我们的系统中有任意的寄存器长度(例如,在FPGA中),我们可以使用Q17.10格式的27位寄存器存储Var2。然而,在C编程中,Var2仍然必须存储在32位寄存器中。如果我们截断Q17.15数字的五个最低有效位并将结果存储在32位寄存器中,我们将得到Q22.10数字。最后,我们可以将c2添加到Var2中,并丢弃10个最低有效位,以得到校准的ADC值,得到方程5:

方程式5。

作为旁注,为了避免任何混淆,我想提到的是,方程4和5中的变量不使用下标,因为这两行被假设为伪代码。例如,文本中的Var2在方程式4和5中表示为Var2。

ADC定点校准验证

让我们看看上述定点系数(c1,new=32422和c2,new=23303)是否可以将测量的ADC响应映射到理想的直线模型。在图1中的A点,ADC输出为437。应用方程式3,Var1为:

将其转换为二进制格式,右移5位,然后找到十进制等效值,我们得到:

现在,我们添加c2、new,并将结果的二进制等效值右移10位,得到:

您同样可以验证点B是否也映射到理想代码3686。请注意,计算机程序使用系数的二进制等效值,我只是使用十进制值来阐明计算。我们同样可以从测量的ADC响应中检查其他点,以确保定点实现产生所需的值。如果不满足这个要求,我们将不得不使用更大的寄存器来存储校准系数。

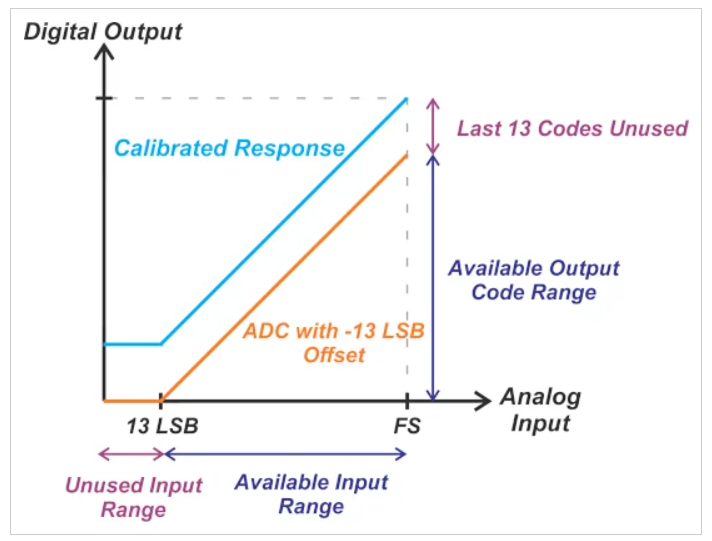

ADC未使用的输出代码和输入范围

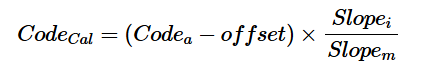

之前,我们讨论过偏移和增益误差会导致未使用的输出代码。上述校准技术是在A/D转换之后执行的。因此,它无法解决未使用的代码问题。为了澄清这一点,请考虑图3中所示的示例。

显示未使用和可用输入范围的示例。

图3。示例显示了未使用和可用的输入范围和输出代码范围。

在这个例子中,显示了一个偏移为-13LSB的单极ADC。通过将ADC读数加13,可以校准偏移误差。但是,请注意,ADC输出小于13 LSB的输入值的全零码。该输入范围在校准响应中仍然不可用,因为校准是在A/D转换后进行的。校准仅向实际ADC响应添加恒定偏移,在上述示例中为低于13LSB的所有值产生代码13。应该注意的是,一些ADC具有与本文讨论的后转换方法不同的内置校准功能。这些内置校准技术可能能够保持ADC的本机范围。这种内置校准技术用于TI的TMS320280x和TMS3202801x设备上的12位ADC。

评论