基于网络编码的多信源组播通信系统,包括源代码,原理图等 (三)

3.4 解码路由器详细设计方案

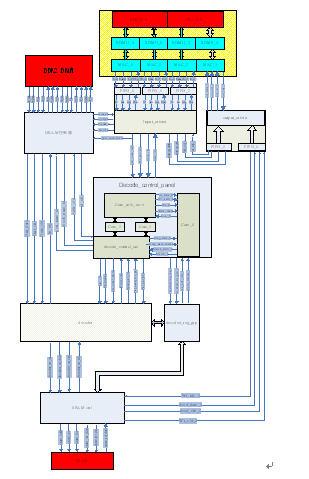

3.4.1 解码路由器系统整体模块图

如下图3.4-1所示,为解码路由器的整体模块图

3.4-1 解码路由器系统整体模块图

3.4.2系统中各单元模块的功能与时序

1、Input_arbiter:采用轮询策略,当fifo非空时从fifo接收数据,根据mac header判断数据是否为IP数据包,若是,则将数据发送到DRAM读写控制模块,同时将信源号、代编号发送到CAM读写控制模块。

可用一个两状态的状态机实现:即轮询判断输入和数据输出:在FIFO非空时读数据,并根据数据包的类型发送到DRAM读写控制器或output fifo中,若是IP数据包,同时将信源号、代编号发送给CAM读写控制。

主要信号列表:

信号名称 | 位宽 bit | I/O | 描述 |

Wr_vld_arb | 1 | 写DRAM控制器有效 | |

Out_data_0 | 64 | 输出至DRAM的data | |

Out_ctrl_0 | 8 | 输出至DRAM德ctrl | |

Src_gen_seq | 24 | 信源号、代的编号 | |

Cam_vld | 1 | 写CAM控制器有效 | |

Port_num_dram | 2 | 数据的接收端口号 | |

Out_data_1 | 64 | 输出至output arbiter的data | |

Out_ctrl_1 | 8 | 输出至output arbiter的ctrl | |

Wr_vld_1 | 1 | 输出至output arbiter信号有效 |

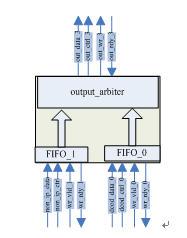

2、output_arbiter

图3.4-2 output_arbiter结构图

本模块的结构如图3.4-2所示,由两个输入fifo和一个输出仲裁器组成,两个fifo缓存来自SRAM和input_arbiter的数据包,Output_arbiter的作用是将解码后的数据发送到MAC层。由于对于非IP数据包我们并没有对其进行编码,所以在解码路由器中由input_arbiter判断后直接输出output_arbiter;对于编码后的IP数据包,在解码后先暂存到SRAM中,再发送出去。本模块就是轮流判断并接收来自SRAM和input_arbiter的数据,并将数据包发送到MAC层。

输入输出信号列表:

信号名称 | 位宽bits | I/O | 描述 |

out_data_3 | 64 | O | 输出至MAC层的数据总线 |

out_ctrl_3 | 8 | O | 输出至MAC层的控制总线 |

out_wr_3 | 1 | O | 输出有效 |

out_rdy_3 | 1 | I | MAC层空闲标志 |

dcod_data_0 | 64 | I | 已经解码的IP数据包的数据总线 |

dcod_ctrl_0 | 8 | I | 已经解码的IP数据包的控制总线 |

wr_vld_0 | 1 | I | 写有效 |

wr_rdy_0 | 1 | O | 接收数据空闲标志 |

non_ip_data | 64 | I | 非IP数据包数据总线 |

non_ip_ctrl | 8 | I | 非IP数据包控制总线 |

wr_vld_1 | 1 | I | 写有效 |

wr_rdy_1 | 1 | O | 接收数据空闲标志 |

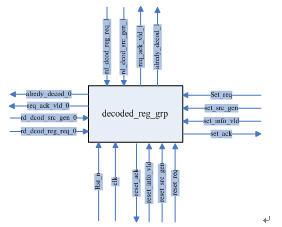

3、decoded_reg_grp

本模块分别与decode_control_panel,decoder和SRAM_contrl相连接,主要作用是记录信源的某代数据包是否已经解码,并将相应的解码信息输出给其他模块,模块结构如图3.4-3:

图3.4-3:decoded_reg_grp模块图

端口列表:

信号名称 | 位宽bits | I/O | 描述 |

rd_dcod_reg_req_0 | 1 | I | 读取解码标志位请求 |

rd_dcod_src_gen_0 | 12 | I | 要读取的数据包的信源号和代编号 |

req_ack_vld_0 | 1 | O | 输出有效 |

alredy_decod_0 | 1 | O | 解码标志(“1”代表已经解码,“0”代表未解码) |

rd_dcod_reg_req_1 | 1 | I | 读取解码标志位请求 |

rd_dcod_src_gen_1 | 12 | I | 要读取的数据包的信源号和代编号 |

req_ack_vld_1 | 1 | O | 输出有效 |

alredy_decod_1 | 1 | O | 解码标志(为1时代表已经解码,为0时未解码) |

set_req | 1 | I | 置位请求 |

set_src_gen | 12 | I | 需要置位的数据包(表示已经解码完毕) |

set_info_vld | 1 | I | 置位信息有效 |

set_ack | 1 | O | 置位请求响应 |

reset_req | 1 | I | 复位请求 |

reset_src_gen | 12 | I | 需要复位的数据包(表示解码后已发送完毕) |

reset_info_vld | 1 | I | 复位信息有效 |

reset_ack | 1 | O | 复位请求响应 |

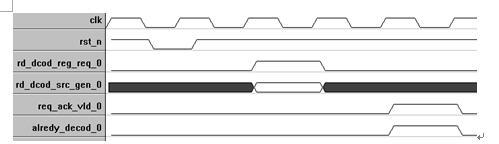

① 读解码标志

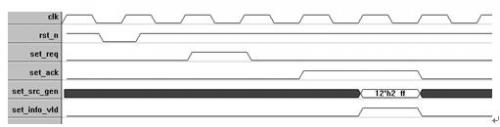

当decoder模块或decode_control_panel读取解码标志时,将查询结果输出,alredy_decod_0和alredy_decod_1为“1”时表示本次查询的数据包已经解码,为“0”时表示未被解码,以与decoder接口为例,读取解码标志的时序如图3.4-4:

图3.4-4:读解码标志位时序图

② 写解码标志位

当decoder把一个数据包解码成功后,就把相应的解码标志位置1,当SRAM_control将一个数据包发送出去后,再将相应的解码标志位置0,以置位为例,解码标志位的写时序如图3.4-5:

图3.4-5:置位解码标志寄存器

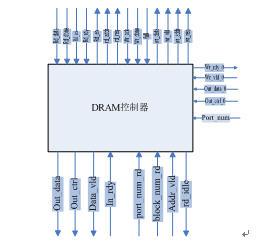

4、DRAM控制器:接收数据,并顺序存储到DRAM中去。

注意:我们将DRAM分为三块,分别对应于数据接收的三个信道,即第0个信道的数据存储到DRAM的第0块,第1个信道的数据存储到DRAM的第1块……信道号由port_num给出。由于DRAM是按照block读写的,因此每个block大小为2034字节,位宽为144位。

图3.4-6:DRAM控制器模块图

① DRAM控制器与DRAM的接口与读写时序:

Signal Group | Signal Name | Direction | Bits | Description |

Request Negotiation | p_wr_req | from user logic to block-of-data rd/wr module | 1 | 1=request for write transfer (data are from user logic to DRAM), 0=otherwise |

Request Negotiation | p_wr_ptr | from user logic to block-of-data rd/wr module | PKT_MEM_PTR_WIDTH | the start address of DRAM for transfer. Each unit is 16-byte piece |

Request Negotiation | p_wr_ack | from block-of-data rd/wr module to user logic | 1 | 1=the arbiter acknowledges that the write requester can proceed, 0=otherwise |

Data Transfer | p_wr_data_vld | from user logic to block-of-data rd/wr module | 1 | 1=the write data is valid, 0=otherwise |

Data Transfer | p_wr_data | from user logic to block-of-data rd/wr module | PKT_DATA_WIDTH | the data transferred from user logic to DRAM |

Data Transfer | p_wr_full | from block-of-data rd/wr module to user logic | 1 | 1=notify the user logic to pause transfer the next clock cycle until this signal is deasserted, 0=otherwise |

Data Transfer | p_wr_done | from block-of-data rd/wr module to user logic | 1 | 1=this is the last write and no more write will be accepted for this block-of-data, 0=otherwise |

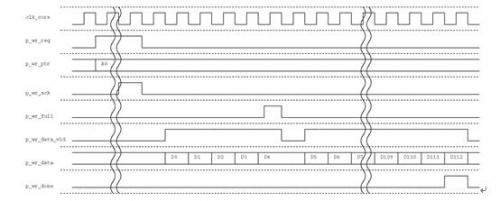

写DRAM时序如图3.4-7:

图3.4-7 写DRAM时序图

读端口:

Signal Group | Signal Name | Direction | Bits | Description |

Request Negotiation | p_rd_req | from user logic to block-of-data rd/wr module | 1 | 1=request for read transfer (data are from DRAM to user logic), 0=otherwise |

Request Negotiation | p_rd_ptr | from user logic to block-of-data rd/wr module | PKT_MEM_PTR_WIDTH | the start address of DRAM for transfer. Each unit is 16-byte piece |

Request Negotiation | p_rd_ack | from block-of-data rd/wr module to user logic | 1 | 1=the arbiter acknowledges that the read requester can proceed, 0=otherwise |

Data Transfer | p_rd_rdy | from block-of-data rd/wr module to user logic | 1 | 1=block-of-data rd/wr module has data for user logic to read, 0=otherwise |

Data Transfer | p_rd_en | from user logic to block-of-data rd/wr module | 1 | 1=user logic reads out one word of data from the block-of-data rd/wr module, 0=otherwise |

Data Transfer | p_rd_data | from block-of-data rd/wr module to user logic | PKT_DATA_WIDTH | data transferred from block-of-data rd/wr module to user logic |

Data Transfer | p_rd_done | from block-of-data rd/wr module to user logic | 1 | 1=this is the last read data and no more data will be read for this block-of-data, 0=otherwise |

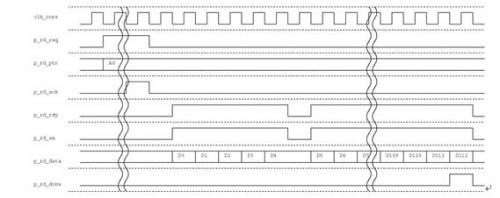

读DRAM时序如图3.4-8:

图3.4-8 写DRAM时序图

② 其他模块对DRAM控制器的读/写过程:

当DRAM读写控制器将一个数据包读/写完之后, 就将rd_idle/wr_rdy_arb置为1,当外部模块需要对DRAM进行读写时,首先要判断这两个信号是否有效,在有效的情况下进行对数据的操作。.端口列表如下:

信号名称 | 位宽bits | I/O | 描述 |

wr_vld_arb | 1 | I | Input_arbiter输入有效 |

out_data_0 | 64 | I | 输入的数据包的data_bus |

out_ctrl_0 | 8 | I | 输入数据包的ctrl_bus |

port_num_dram | 2 | I | 输入信号的端口号,指明数据存放在DRAM的区域 |

wr_rdy_arb | 1 | O | 写空闲信号 |

port_num_rd | 2 | I | 读取数据包的区域 |

addr_vld | 1 | I | 读地址有效 |

block_num_rd | 8 | I | 数据包存放的block的起始地址 |

rd_idle | 1 | O | 读空闲信号 |

in_rdy | 1 | I | 数据输出输出允许信号 |

out_data | 64 | O | 读出的数据包的data_bus |

out_ctrl | 8 | O | 输出数据包的ctrl_bus |

data_vld | 1 | O | 输出数据有效 |

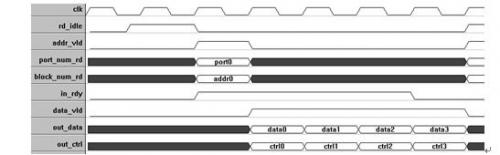

(1)当decode_control_panel对DRAM控制器进行读操作时,将信道号和block地址发送至DRAM控制器,接着DRAM控制器从DRAM中读取数据,当decoder空闲时将数据发送出去,时序图如3.4-9所示:

图3.4-9 对DRAM控制器的读操作

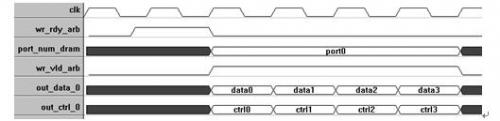

(2)当DRAM控制器进行写操作时,将按照input_arbiter发送过来的端口号,按照地址大小顺序写DRAM,时序图如3.4-10:

图3.4-10 对DRAM控制器的写操作

5、decode_control_panel

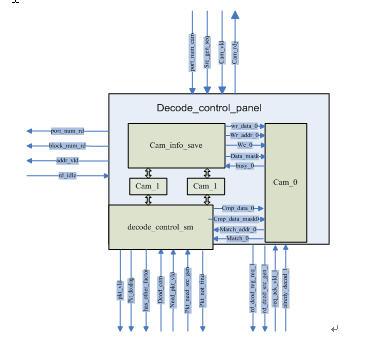

① 本模块的内部结构图如3.4-11所示,它由以下五个模块组成:cam_info_save, decode_control_sm和3个CAM组成。

图3.4-11:decode_control_panel内部结构图

本模块的输入输出端口定义表如下:

端口名称 | 位宽 bits | I/O | 描述 |

port_num_cam | 2 | In | 数据写入的CAM号,即信道号 |

Src_gen_seq | 24 | In | 输入数据包的信源号、代编号 |

Cam_vld | 1 | In | 写有效 |

Cam_rdy | 1 | Out | 写Cam准备好 |

rd_idle | 1 | In | DRAM准备好 |

block_num_rd | 8 | Out | 读DRAM的地址 |

addr_vld | 1 | Out | 读地址有效 |

port_num_rd | 2 | out | 要读取的DRAM的编号 |

Pkt_vld | 1 | Out | 要解码的数据包输出有效标志 |

Pkt_decoding | 12 | out | 正在解码的数据包的信源号、代编号 |

Decod_com | 1 | In | 数据包解码完成标志 |

has_other_factor | 1 | Out | 有另外一个解码因子 |

Pkt_not_find | 1 | Out | 所需要解码数据包未找到 |

pkt_need_src_gen | 12 | In | 解码需要的数据包 |

need_pkt_vld | 1 | In | 所需数据包有效 |

rd_dcod_reg_req_1 | 1 | Out | 读解码标志寄存器请求 |

req_ack_vld_1 | 1 | In | 标志位有效 |

Alredy_Decod_1 | 1 | In | 解码标志位 |

rd_dcod_src_gen_1 | 12 | out | 查询数据包是否已经解码 |

② cam_info_save:

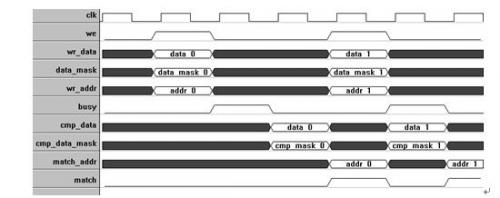

该模块的主要功能是将输入的数据包的信源号和代的编号按地址大小顺序存入到三个cam中,每个cam分别对应于三个数据输入通道。每个CAM的大小是24bits×256,我们要求CAM的读写操作可以同时进行,写数据从DIN进入,而读(查询)的数据从CMP_DIN进入,写操作时BUSY信号有效,表示不可以响应其他写请求,图3.4-12是一个CAM的读写操作时序:

图3.4-12:CAM读写过程

评论