基于网络编码的多信源组播通信系统,包括源代码,原理图等 (三)

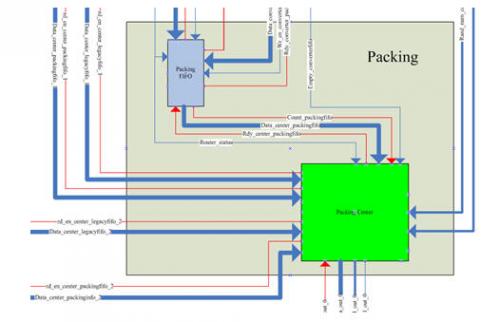

4、Packing

① 子模块列表

Sub module name | quantity | Description |

Packing FIFO | 1 | Receive and store processed packets before being packed in “packing center” |

Packing center | 1 | Packing payload with all sorts of heads |

② 内部结构图

图3.2-8 Packing内部结构图

③ 本模块输入输出信号列表及说明

Signal name | Bit width | I/O | Description |

Data_router_packingfifo | 73 | input | Input data bus from “payload router”. Bit 64 is set to “0” to indicate this is an uncoded packet |

Wr_en_router_packingfifo | 1 | Input | Write enable |

Rdy_router_packingfifo | 1 | Output | 1=module “packing FIFO” is ready to receive from payload router, 0=otherwise |

Router_status | 3 | input | Input FSM state signal to coordinate with the control of “packing FIFO” |

Empty_packingfifo | 1 | output | 1=FIFO packing is empty,0=otherwise |

Data_converter_packingfifo | 73 | input | Input data bus from “m72to64 converter”. Bit 64 is set to “1” to indicate this is a coded packet |

Wr_en_converter_packingfifo | 1 | Input | Write enable |

Rdy_converter_packingfifo | 1 | Output | 1=module “packing FIFO” is ready to receive from m72to64 converter, 0=otherwise |

Empty_converterfifo | 1 | Input | 1=FIFO converter is empty,0=otherwise |

Data_center_legacyfifo_1 | 64 | Input | Input data bus from “FIFO ctrl legacy 1” |

Rd_en_center_legacyfifo_1 | 1 | output | Read enable |

Data_center_packinginfo_1 | 14 | Input | Input data bus from “FIFO ctrl packinginfo 1” |

Rd_en_center_packinginfo_1 | 1 | output | Read enable |

Data_center_legacyfifo_2 | 64 | Input | Input data bus from “FIFO ctrl legacy 2” |

Rd_en_center_legacyfifo_2 | 1 | output | Read enable |

Data_center_packinginfo_2 | 14 | Input | Input data bus from “FIFO ctrl packinginfo 2” |

Rd_en_center_packinginfo_2 | 1 | output | Read enable |

Rand_num_center_1 | 8 | input | Input random number from “m64×64 multiplier 1” |

Rand_num_center_2 | 8 | input | Input random number from “m64×64 multiplier 2” |

Out_data_out_0 | 64 | output | Output data bus to “output arbiter” |

Out_ctrl_out_0 | 8 | Output | Output ctrl bus to “output arbiter” |

Data_val_out_0 | 1 | Output | 1=data from packing center to output arbiter is valid, 0=otherwise |

Rdy_out_0 | 1 | Input | 1=output arbiter is ready to receive from packing center, 0=otherwise |

clk | 1 | Input | System clock running at 125 MHz |

Rst_n | 1 | input | System asynchronous reset signal |

④ 功能描述及数据流

本模块为封装模块。子模块packing FIFO构建与coding模块的数据接口,将接收并缓存编码数据包以及未编码数据包(使用额外第64位数据标志该包是否编码,该位为“1”说明编码,该位为“0”说明未编码)。

子模块packing center是主封装模块。它根据packing FIFO中读出的数据判断需要哪些包头信息,然后向control模块中相应FIFO读取需要的包头信息,并依次封装成NCP数据包,发送到output arbiter。

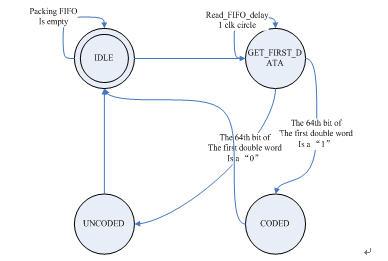

⑤ 关键时序及状态机

Packing center状态机

第一层状态机:packing_center_status

图3 .2-9 packing_center_status状态机

第二层状态机:

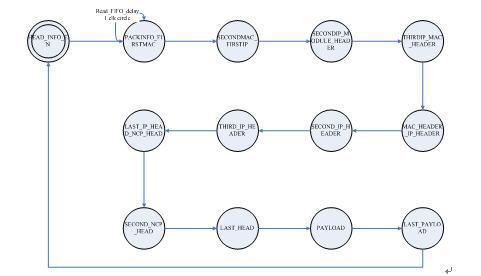

coded_process

图3 .2-10coded_process状态机

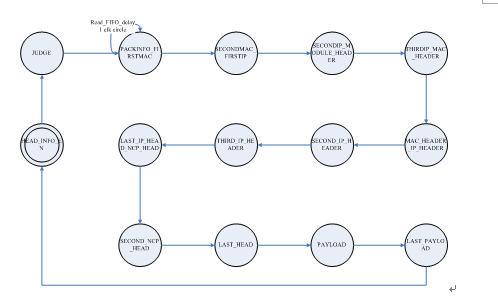

uncoded_process

图3.2-11 uncoded_process 状态机

5、Output arbiter

① 本模块输入输出信号列表及说明

Signal name | Bit width | Input or output | Description |

Out_data_out_0 | 64 | input | input data bus from “packing center” |

Out_ctrl_out_0 | 8 | Input | input ctrl bus from “packing center” |

Data_val_out_0 | 1 | Input | 1=data from packing center to output arbiter is valid, 0=otherwise |

Rdy_out_0 | 1 | output | 1=output arbiter is ready to receive from packing center, 0=otherwise |

Out_data_out_1 | 64 | input | input data bus from “input arbiter 1” |

Out_ctrl_out_1 | 8 | Input | input ctrl bus from “input arbiter 1” |

Data_val_out_1 | 1 | Input | 1=data from input arbiter 1 to output arbiter is valid, 0=otherwise |

Rdy_out_1 | 1 | output | 1=output arbiter is ready to receive from input arbiter 1, 0=otherwise |

Out_data_out_2 | 64 | input | input data bus from “input arbiter 2” |

Out_ctrl_out_2 | 8 | Input | input ctrl bus from “input arbiter 2” |

Data_val_out_2 | 1 | Input | 1=data from input arbiter 2 to output arbiter is valid, 0=otherwise |

Rdy_out_2 | 1 | output | 1=output arbiter is ready to receive from input arbiter 2, 0=otherwise |

Out_data_mac | 64 | output | output data bus to “MAC Layer” |

Out_ctrl_mac | 8 | Output | output ctrl bus to “MAC Layer” |

Data_val_mac | 1 | Output | 1=data from output arbiter to MAC layer is valid, 0=otherwise |

Rdy_mac | 1 | Input | 1=MAC layer is ready to receive from output arbiter, 0=otherwise |

clk | 1 | Input | System clock running at 125MHz |

Rst_n | 1 | input | System asynchronous reset signal |

② 功能描述及数据流

本模块为输出仲裁模块。为协调多路输出通道,避免冲突而设计。入端构建与input arbiter通信的两路端口和与packing通信的一路端口,出端构建与MAC层通信的输出端口。将选通并维护唯一一条输入通道直至该数据包全部发送完毕。采用轮询方式检查三路输入通道以避免冲突。

③ 关键时序及状态机

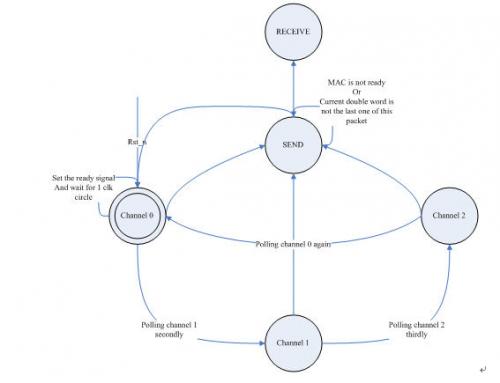

图3.2-12 Output arbiter状态机

3.3 转发路由器详细设计方案

3.3.1转发路由器系统整体模块图

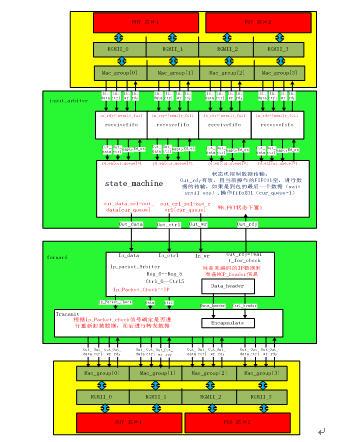

图3.3-1总体模块图

系统模块功能说明:该模块有两个子模块input_arbiter模块和forward模块构成,其中前者为标准模块;后者为自定义模块,接受来自MAC层的数据包,经过相关处理输出数据包,实现将未编码的IP数据包封装成NCP数据包并进行转发以及将其它非IP数据包或NCP数据包进行直接转发的功能。

3.3.2系统中各单元模块的功能与时序

Input_arbiter模块

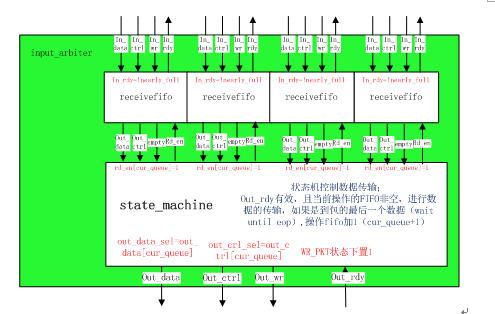

① Input_arbiter模块的内部结构图如图3.3-2

图3.3-2 input_arbiter模块

② 本模块的输入输出信号列表及说明(如下例)

信号名称 | 位宽 bits | I/O | 描述 |

in_data_n(n:0、1、2、3) | 64 | input | 从MAC层输入的data数据 |

in_ctrl_n(n:0、1、2、3) | 8 | input | 从MAC层输入的ctrlbus数据 |

in_wr_n(n:0、1、2、3) | 1 | input | 从MAC层输入的数据写使能信号(1为有效) |

in_rdy_n(n:0、1、2、3) | 1 | output | 输出至MAC层的准备信号(1为准备完毕,可以写入) |

out_data | 64 | output | 输出至forward模块的data数据 |

out_ctrl | 8 | output | 输出至froward模块的ctrl数据 |

out_wr | 1 | output | 输出至forward模块的写使能信号(1为写使能有效) |

out_rdy | 1 | input | 从forward模块输入的准备信号(1为准备好,可以写入) |

本模块的功能描述以及内部数据处理的过程

功能描述:从MAC层的接口传来的数据信号写入到receivefifo中,每个接口接一个fifo,通过本模块的仲裁,循环查询每个fifo,如果每个fifo不为空则输出该fifo的数据到forward 模块。本次实验只用到接口1,其他接口实际上是没有数据输入,然而为了以后的可拓展设计,采取循环查询每个fifo,这样可以从每个接口进行数据读入数据,更合理。

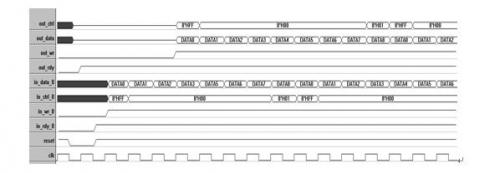

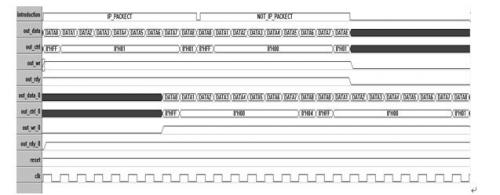

④ 关键时序和状态机转化图

图3.3-3 input_arbiter时序图

2、forward模块

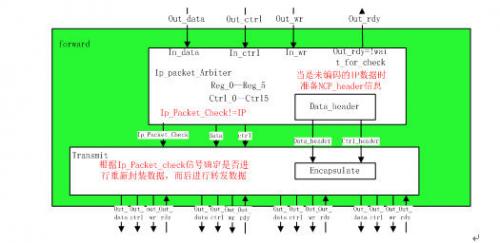

① forward模块的内部结构图如图3.3-4

图3.3-4

②本模块的输入输出信号列表及说明(如下例)

信号名称 | 位宽 bits | I/O | 描述 |

out_data | 64 | input | 从input_arbiter模块输出的data数据 |

out_ctrl | 8 | input | 从input_arbiter模块输出的ctrl数据 |

out_wr | 1 | input | 从input_arbiter模块输出的写使能信号(1为写使能有效) |

out_rdy | 1 | input | 输出至input_arbiter模块的准备使能信号(1为准备使能有效) |

out_data_n(n:0、1、2、3) | 64 | output | 输出至MAC层的data数据 |

out_ctrl_n(n:0、1、2、3) | 8 | output | 输出至MAC层的ctrlbus数据 |

out_wr_n(n:0、1、2、3) | 1 | output | 输出至MAC层的数据写使能信号(1为有效) |

out_rdy_n(n:0、1、2、3) | 1 | intput | 从MAC层输入的准备信号(1为准备完毕,可以写入) |

③ 本模块的功能描述以及内部数据处理的过程

(1)Forward模块下子模块Ip_Packet_Arbiter 定义6个寄存器变量分别为:Reg_0—Reg_5 宽度为64bit, 6个寄存器变量:Ctrl_0—Ctrl_5宽度为8bit.分别存储数据包的前48个字节数据和CtrlBus信息。以便对包头进行解析,并进行判断所属的类型。

(2)判断属于哪一类型的数据包,如果是非IP数据包则从Ip_packet_Arbiter模块发送一个信号Ip_Packet_Check的信号到Transmit模块,通过data信号线和ctrl信号线将数据传送到Transmit模块并转发到各个接口;

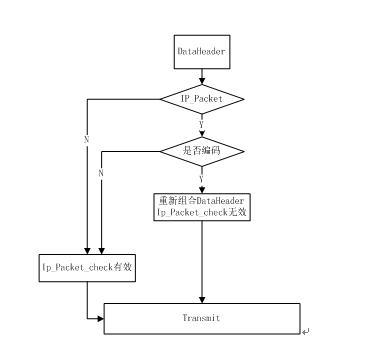

(3)如果属于iP数据包则进一步判断是属于编码后的数据包还是未编码的数据包,如果是编码后的数据包则和①做同样处理,如果是未编码的数据包,则进行相应的处理(更改modulheader、MAC的目标地址、Ip包头、添加NCP包头操作),然后将组合好的数据包头和Ctrlbus 和Ip_Packet_Check信号一起送到Transmit模块。在Transmit模块通过收到的Ip_Packet_Check信号进行判断是否需要对存放数据进行重新的封装并进行相应处理,然后进行转发操作。整个过程的流程图如图3.3-5

图3.3-5

④关键时序和状态机转化图

图3.3-6

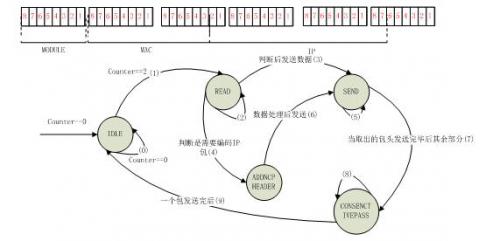

⑤ froward模块下子模块Transmit的状态机以及描述如图3.3-7

图3.3-7

对整个状态机工作条件进行详细的描述如下:

当满足满足计数器counter=0的条件时,进入IDLE状态;counter计数器不改变并且不是包头的起始信号时则保持在该状态;如果counter=1,发现包头起始信号则保存该字段的值,并设置counter=2;

当满足计数器counter=2时,并且是包的中间值信号时则跳转到READ状态;根据counter计数器的值有条件的保存在该状态;counter自加;

当满足计数器counter=3时,判断MAC字段中上层协议的类型标志,如果为IP数据包继续保持在READ状态,counter+1;当counter=4时 进行判断数据包中协议字段的如果为未编码的IP数据包则保存在该状态,counter+1;

当满足counter=3时判断上层协议类型标志为非IP数据包,则直接跳转到SEND状态;如果为已经编码的IP数据包既NCP数据包,则调整到SEND状态;

当counter=7的时候,跳转到ADDNCPHEADER状态;数据处理完毕后state=SEND;

当暂存的数据包没有发送完之前则保持在该状态;

当state=SEND时,跳转到SEND状态;

当暂存的数据包的字段发送完毕后,跳转到CONSENCTIVEPASS(持续发包)状态时;

判断包尾的结束标志,如果不是包尾的结束标志则保持在该状态;

判断包尾的结束标志,如果是包尾的结束标志,则发最后一个字段,并跳转到IDLE(起始状态);

评论