如何验证和分析复杂的串行总线链路模型

用于DDR的链路分析技术

链路分析传统上是针对高速串行应用;不过,在串行链路中使用的技术在其他领域(包括DDR内存)也能获得成功。通常,DDR信号是使用高阻抗探头来存取的,这会导致采集波形上的反射。链路分析软件可用于仿真对不同测试点的探测和消除由测量电路及不良信号存取点造成的反射。

图8显示了一种典型情景。采集波形存在由传输线和接收器输入之间的阻抗失配而造成的严重反射。如果不对采集波形进行任何后处理,则不可能对信号进行分析。

图8:由于传输线与接收器之间的阻抗失配,不可能对该DDR信号进行分析。

如前所述,为了去嵌反射,发射器、通道和接收器模型必须是已知的。但现实中常常难以获得针对所有链路元件的模型,在上面的情形中,可使用近似法来补偿采集信号上的反射。传输线时延和接收器负载阻抗可通过执行简单的定时和电压测量来估计。通过使用游标,可按下式计算反射/入射电压比:

在图7所示的波形中,V2 = 1.2V,V1 = 0.75V。因此,我们能够估计RX输入阻抗大概在200Ω。下一步是估计从实际探测位置到期望测量点的传输线时延。通过使用游标,得到往返反射时间660ps(如图9所示)。为了确定探测点与期望测试点之间的时间,我们将此数值除以2。

图9:带游标的DDR信号可用于测量往返反射时延,以近似实际探测位置与RX输入之间的传输线时延。

使用链路分析工具,我们能够估计测试点大概是在接收器的输入位置。这是通过指定传输线时延、接收器的封装模型以及接收器的输入阻抗来进行的。在此情形中,接收器的封装模型由一个4端口S参数模型定义。如果发射器、接收器和传输线的精确模型已知,则最终结果(如图10所示)会更准确。不过,基于使用上面的技术,结果精确性已足以对信号进行分析,包括测量和协议解码。

图10:在使用串行数据链路分析工具消除了反射之后和在RX输入位置进行探测仿真之后,现在能够对DDR信号进行分析了。

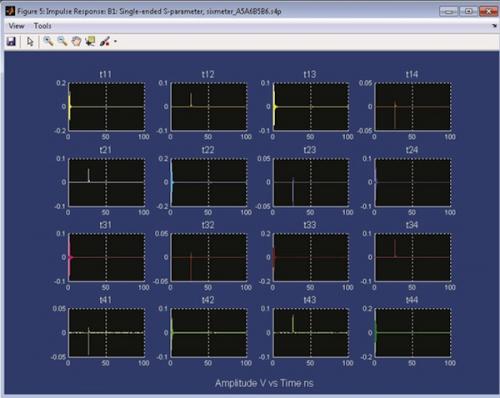

图11显示了上述每个S参数向量的时域脉冲响应表示。这也是一个很有用的视图,因为它能容易地显示传输项的时延。它还会显示数据是否是在该时间间隔内建立的,因为非如此不能保证S参数集的有效性。这些曲线是通过计算频域S参数数据IFFT(快速傅里叶逆变换)而得到的。这常常需要把频域数据外推至DC,有时需要外推至更高的理想Nyquist频率。

图11:数据链路的4端口S参数集的时域图也是一个很有用的视图,因为它能容易地显示传输线的时延。

本文小结

随着信号传输速度增加和几何形状缩小,强大的串行数据链路分析变得日益重要。通过使用S参数、传输线或RLC模型来创建在每个测试点的波形传递函数,此类应用程序能够更新示波器显示屏上的实况仿真测试点波形。可以在感兴趣的测试点上执行各种功能,包括协议解码、抖动和眼图分析或者数学函数。这是使用实时示波器上的链路分析软件直接实现的。如本文所述,链路分析能够实现各种目标,包括去嵌测量电路,以便在TX引脚位置测量DUT,应用硅芯片专属均衡来使眼图张开,以及消除由于非理想实际探测位置而产生的反射。

评论