利用Xilinx FPGA和分解器数字转换器简化角度测量

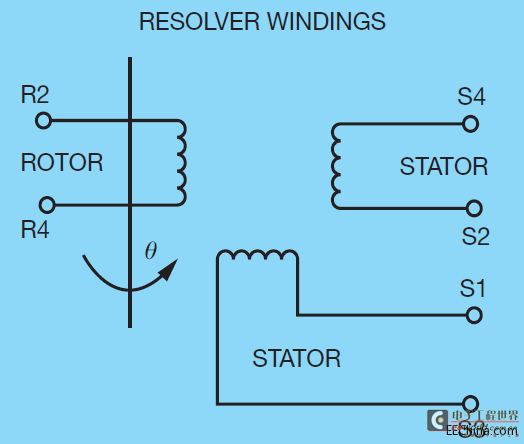

分解器的定子输出电压为:

V1= V sinωt sinθ方程1

V2= V sinωt cosθ方程2

其中θ是分解器转子的角度。数字角度ψ应用到余弦乘法器,其余弦乘以V1得出下式:

V sinωt sinθ cosψ 方程3

数字角度ψ另外还应用到正弦乘法器,乘以V2得出下式:

V sinωt cosθ sinψ 方程4

这两个信号由误差放大器相减求得出波形的误差信号:

(V sinωt sinθcosψ – V sinωt cosθ sinψ) 方程5

V sinωt (sinθ cosψ- cosθ sinψ) 方程6

根据三角恒等式,其简化为:

V sinωt [sin (θ -ψ)] 方程7

本文引用地址:https://www.eepw.com.cn/article/201702/338336.htm

图3 – SD-14620方框图(单信道)

图中文字如下:

REFERENCE CONDITIONER:基准调节器

BIT DETECTOR:位检测器

“S” OPTION SYNTHESIZED REFERENCE:“S”选项综合基准

INPUT OPTION:输入选项

CONTROL TRANSFORMER:控制变压器

GAIN:增益

DEMODULATOR:解调器

HYSTERESIS:滞后

INTEGRATOR:积分器

DC/DC CONVERTER:DC/DC转换器

14/16 BIT UP/DOWN COUNTER:14/16位递增/递减计数器

VCO & TIMING:VCO与时序

DATA LATCHES:数据锁存器

FILTER:滤波器

47μf external capacitor:47μf外部电容

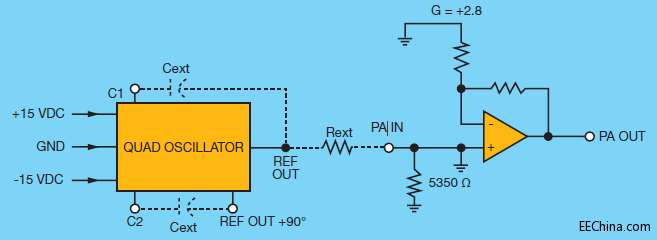

图4 – OSC-15802基准振荡器方框图

图中文字如下:

QUAD OSCILLATOR:四线组振荡器

检测器采用分解器的转子电压作为基准同步解调此AC误差信号。这会产生与sin (θ -ψ)成正比的DC误差信号。

DC误差信号馈送到积分器,其输出驱动一个由电压控制的振荡器。而VCO会导致递增/递减计数器按正确方向计数,从而在一次计数中产生:

sin (θ -ψ)→0方程8

当取得此结果,则:

θ -ψ→0 方程9

因此,

θ = ψ 方程10

因此,计数器的数字输出ψ代表着角度θ。锁存器可以在不中断回路跟踪情况下实现此数据向外部的传输。

此电路等效于2型伺服回路,因为它实际上有两个积分器。一个是累计脉冲的计数器;另一个是位于检测器输出端的积分器。在具有恒定旋转速度输入的2型伺服回路中,输出数字字连续跟随或跟踪该输入,而无需外部导出转换。

RDC典型实例:SD-14621

SD-14621是数据设备公司(DDC)生产的小型低成本RDC。它有两条具备可编程分辨率控制功能的信道。分辨率编程功能允许选择10、12、14或16位模式[4]。此功能允许低分辨率高速跟踪或者更高分辨率支持更高精度。由于其大小、成本、精度与多功能性,此转换器适用于高性能军用、商用及位置控制系统。

器件的运行需要一个+5V电压。转换器有两个对模拟地为±4V电压范围的速度输出(VEL A、VEL B),可用于替代转速计。为两条信道(/BIT A与/BIT B)提供两个内置测试输出,以指示信号丢失(LOS)。

此转换器由三大部分组成:输入前端、误差处理器和数字接口。前端对于同步器、分解器和直接输入端有所不同。电子Scott-T用于同步器输入,分解器调节器用于分解器输入,而正弦与余弦电压跟随器用于直接输入端。这些放大器可以馈送高精度控制变压器(CT)。CT的另一个输入是16位数字角度ψ,其输出是两个输入之间的模拟误差角度或差分角度。CT采用放大器、交换机、逻辑电路与电容器以查准率执行SINθ COSψ - COSθ SINψ = Sin(θ-ψ)的三角函数计算。

与常规精密电阻器相比,这些电容器按查准率使用,以获得更高精度。另外,这些电容器(与运算放大器一起用作计算元件)进行高速采样,以消除偏移和运算放大器偏差。

DC误差处理进行积分运算,然后得到驱动电压控制振荡器的速度电压。此VCO与速度积分器结合在一起构成递增积分器:一种2型伺服反馈回路。

基准振荡器

我们设计中采用的OSC-15802功耗振荡器也是DDC公司提供。此器件适用于RDC、同步器、LVDT和感应式传感器应用[5]。频率与振幅输出可以分别由电容器和电阻器编程。输出频率范围介于400Hz~10kHz之间,输出电压为7Vrms。图4显示了器件的方框图。

馈送到分解器和RDC的振荡器输出用作基准信号。

FPGA的I/O电压为3.3V,而RDC的电压为5V。我们采用电压收发器实现两个器件之间的电压兼容。

VIRTEX-5 FX30T FPGA与RDC接口

我们在设计中采用赛灵思Virtex-5 FX30T FPGA [6]。FPGA的I/O电压为3.3V,而RDC的电压为5V。因此我们采用电压收发器来实现这两个器件之间的电压兼容。通过赛灵思提供的GPIO IP核与FPGA建立内部连接,如图5所示。

为了简单起见,图5仅显示一条具有一个分解器接口的信道。您可以在本文件随附的赛灵思开发板描述(XBD)文件找到RDC的引脚详情以及FPGA对应的专用引脚。详情见该文件第一部分。

评论