关于高速多通道虚拟逻辑分析仪

3.2 触发控制实现原理

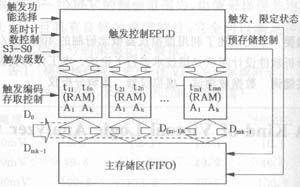

由数据存储原理知,逻辑分析仪FIFO数据正确存储的关键之一是对trw的控制,即通过触发识别实现起始、终止、延迟(时钟、事件)、随机、序列、组合和限定等触发控制。利用位存储映射方法,采用高速EPLD[3]与触发存储器结合,设计的实现触发控制的原理框图如图2所示。

图2中,D0~Dmk-1为被测数据。触发RAM数据位宽为n,地址宽度为k,个数为m,故可观测的数据流的宽度为m·k。当k≥n时,最大序列触发或组合触发识别级数L为:

L≦2n-1 (7)

图2 触发控制实现原理框图

4 系统软件设计

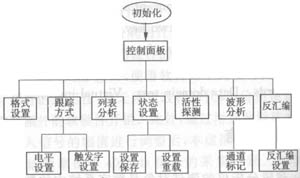

利用图像界面操作系统Windows和以Windows为基础的可视化程序设计平台C++Builder,软件由15个窗体加5个单元文件组成,各主要窗体之间的关系如图3所示。

图3 系统软件各窗体及相互关系

5 结束语

逻辑分析仪结构复杂,技术要求高。本文所述的基于虚拟仪器概念的设计思想和方法,因部分硬件功能软化而使硬件电路大为简化,同时采用了EPLD器件,从而降低了仪器成本,提高了仪器的可靠性和性能,且功能易于扩展。400MHz/102通道逻辑分析仪已于2000年12月28日通过了信息产业部军工预研局主持的技术鉴定。

评论