数字下变频FFT及其在频谱分析仪中的实现

|

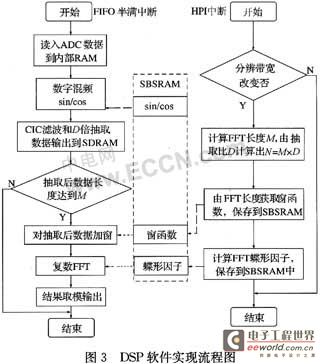

图3是其DSP基于中断响应的软件实现流程图,该DSP软件主要由2个中断处理程序共同完成。其中,2个中断分别为HPI中断和FIFO半满中断。

|

主机的HPI中断通过访问DSP的HPI接口产生,该中断用来通知DSP得到当前频谱分析仪的分辨率,并根据式(2)由分辨率、窗函数-3 dB带宽因子K和采样率计算出FFT长度M,并由预先设定的抽取比D计算出采样数据长度N=M×D。

FPGA控制产生的ADC采样FIFO半满中断,则先让DSP完成数据采集、软件数字下变频;当所采集的数据足够时,再进行FFT处理(此时FPGA控制ADC停止采样)。由于DSP片内数据空间较小,ADC采样数据先保存在内部RAM,经CIC抽取滤波后,其输出数据和FFT处理数据都存放在外部SDRAM空间,而SBSRAM是参数存放和传递的空间,里面包括数字本振(该数据是在开机时由主机加载)、窗函数和FFT蝶形因子等参数。

4 处理时间比较与分析

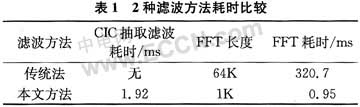

本文选择在相同ADC采样数据下将传统FFT和数字下变频FFT 2种方法的处理时间进行对比测试,在测试中选择的采样数据量为64K,基于数字下变频的FFT方法选择的抽取比为64,所有FFT数据访问都是在片外SDRAM,测试结果如表1所示。

|

由表1可以知,基于数字下变频的FFT方法总共耗时为1.92+0.95=2.87 ms,远小于传统法的320.7 ms。传统法处理时间过长,主要是因为FFT算法本身的大数据量运算耗时较多,而且DSP访问外部SDRAM较之片内耗时更多。64K数据都在外部SDRAM,而FFT算法需要多次对数据进行读写操作,这必然导致整个处理中的数据访问时问增加,从而引起整个处理时间增加。相比而言,基于数字下变频的FFT方法只需进行1K点的FFT;而且CIC抽取滤波处理是在片内进行的,均是简单的加法运算,整个处理时间自然就少多了。

5 结 论

本文分析了基于数字下变频的FFT技术的具体方法,在实现宽带频谱分析和窄的分辨率方面,该方法比传统的FFT更能有效降低整个处理过程的运算量、存储量和处理时间。实际应用证明:在某新型频谱分析仪中,通过在单片DSP里的软件实现,并由处理时间对比测试可知,该方法较之传统FFT方法能大幅度提高系统的实时性。

评论