CPRI协议分析仪的硬件开发与实现

|

|

实际信号测试

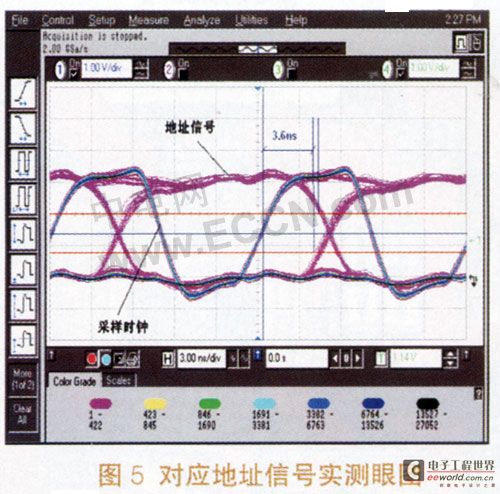

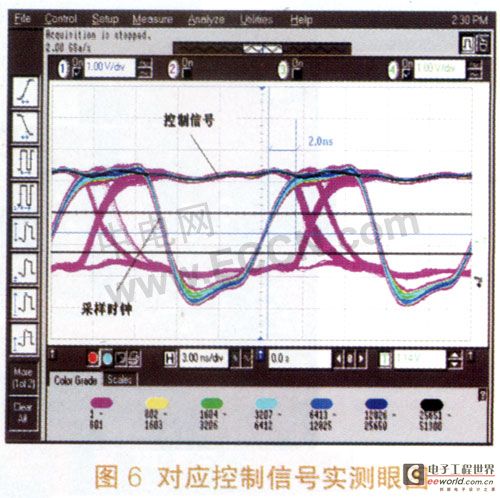

控制信号的实测眼图及其与采样时钟的相位关系见图5、图6。

|

根据实测数据推算,地址信号和数据信号在SDRAM处的采样时间裕度分别为2.8ns和1.2ns,与仿真计算结果一致。

结论

通过严格的信号仿真和时序裕度计算,实时的调整设计和对板卡的布局布线优化后,板卡性能表现良好,同时也减少了PCB的改版设计次数,节约了研发成本。在GHz级的设计中,PCB的设计非常重要,传输线的特性阻抗控制,过孔的特性阻抗控制,端接匹配的设计对信号的影响不容忽略。对于过孔,由于成本和性能上需要均衡,多层板卡的 无用焊盘引入的电容负载增大,在后续的EDA制图工具中,支持中间层多余焊盘删除的功能是必需的。随着板卡集成度的提高,仿真计算等工作越来越显得必要,凭经验设计的年代逐渐久远,可预知的、可控制性设计需要渗透到每一个细节。

评论