支持ASIL D 应用的安全集成硬件解决方案

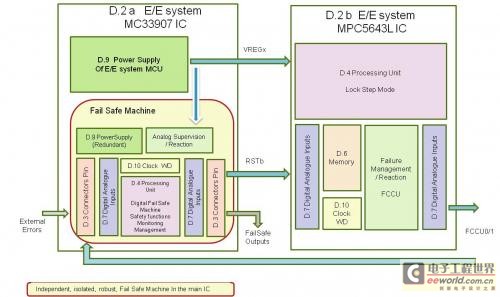

这两个系统 IC 中所用的专用半导体元件请参考 ISO 26262-5:2011(E) 附录 D 中 D.1 至 D.10(见图 5)。 这有利于分解元件并指示诊断覆盖范围。

图5:飞思卡尔功能安全系统解决方案(包括 ISO26262 附录 D 方法)

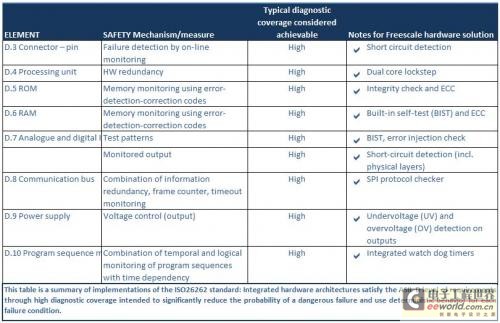

下表汇总的内容如下:

- 飞思卡尔安全系统中的硬件元件列表

- 为各个元件实施的安全机制/措施

- 各个安全机制/措施可实现的典型诊断覆盖范围,请参见 ISO 26262-5:2011 (E) 附录 D

资料来源: 参考 ISO 26262-5:2011 (E) 附录 D 与飞思卡尔硬件解决方案(MPC5643L 与 MC33907)。

表1 MC33907 和 MPC5643L 的组合值满足 ASILD 要求

SafeAssure MCU和模拟系统基础芯片组合在一起可视为一个 SEooC,有利于评估系统安全性。这些器件的开发是为了支持 ISO 26262 标准要求,并提供了一种可扩展的方法,以简便地开发需要遵从功能安全标准的系统。各个元件之间的最佳交互使系统更简单、更强大。此外,这种架构能够减少系统级组件的数量,满足功能安全需求,并增强可靠性。

在 MC33907 内部,电源管理单元和自动防故障装置相结合,与 MCU 进行交互。采取 4 个安全措施,确保 MCU 和 SBC 无中断电源之间的交互,故障安全输入监控关键信号,故障安全输出驱动故障安全状态,而看门狗用于先进的时钟监控。当与 MPC5643L MCU 相结合时,每个安全措施可以进行优化,以实现最高的安全性能水平。

在组件开发过程中,开发一个完整的失效模式、效应和诊断分析(FMEDA),根据单点故障、潜在故障和共因失效(CCF)测量安全性能。此类安全分析是 SafeAssure产品的支持交付项的一部分,也是混合设备失效模式分析的结果,可确定系统是否安全。设备架构已经实施,具体目标是降低 FMEDA 风险。

例如,分离主要功能(供电和通信)和自动防故障机(一组独立的安全功能,如监控、检测和安全状态控制)可降低 CCF。已经采取了这一具体措施来降低 CCF,并结合了模拟和数字内置自测(BIST)功能,这有助于减少潜在故障。

在系统级,MPC5643L 提出的安全检查机制可由 MC33907 通过故障采集控制单元 (FCCU) 的双稳协议来监控。这种 IC 交叉检验,如对监控定时的查询等,可对系统进行外部检测,作为额外的措施,进一步确保故障检测。

为了符合系统基础芯片系列的安全架构,可以通过一个专用的故障安全输出为安全状态激活提供冗余路径。当发生故障情况时,这些输出将应用设置为确定性状态,以弥补 MCU 故障安全输出。

这些硬件实施方案帮助软件工程师简化了软件架构,且实施的软件开发策略侧重于使用单一的 MCU 方法来确保安全性。

最后,提供了详细的文档,该文档描述了功能安全、安全目标和各个组件的安全实施方案,因此可使用标准的半导体设备管理各种安全应用。

结论

从措施和架构角度来看,在芯片级实施与安全相关的功能所用的新的 ISO 26262 标准尚处于初级阶段。 在冗余和简易性之间取得恰当的平衡是开发经济高效而安全的解决方案的关键。

使用各种类型的架构都有可能达到 ASIL-D 级要求,但是,正确实施 MCU 和 SBC 可让系统更简单、速度更快、更可靠和更具成本效益。MC33907 SBC 和 MPC5643L MCU 相结合,可使设计人员将飞思卡尔的SafeAssure流程融合到硬件、软件和支持中,从而更轻松地将功能安全添加到关键系统中。这些器件的结合以及全面的文档(如 FMEDA 和“安全手册”)旨在简化硬件架构,并加快任何 ISO 26262 应用的面市速度。

飞思卡尔的独特方法旨在简化功能安全,降低风险并降低开发过程的成本。在生产之前的开发流程的早期预测风险并降低潜在故障的影响,有助于提高驾驶员和乘客的安全,还能够降低制造商的质量成本。

评论