SPI总线之CPOL CPHA

【 CPHA相位】

本文引用地址:https://www.eepw.com.cn/article/201612/330521.htm首先说明一点,capture strobe = latch = read = sample,都是表示数据采样,数据有效的时刻。

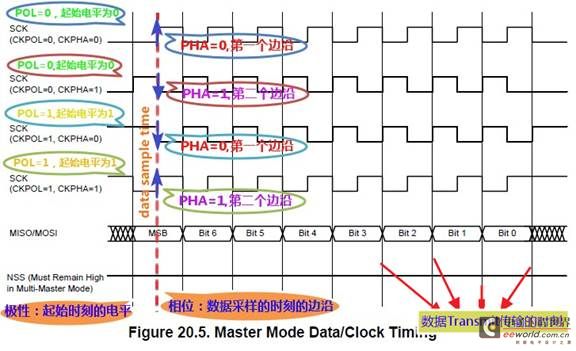

相位,对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,0对应着第一个边沿,1对应着第二个边沿。

对于:

CPHA=0,表示第一个边沿:

对于CPOL=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;

CPHA=1,表示第二个边沿:

对于CPOL=0,idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从低变到高,所以是上升沿;

用图文形式表示,更加容易看懂:

此处,再多解释一下可能会遇到的CKP和CKE,其是Microchip的PIC系列芯片中的说法。

(1)CKP是Clock Polarity Select,就是极性=CPOL:

CKP,虽然名字和CPOL不一样,但是都是指时钟相位的选择,定义也一样:

CKP: Clock Polarity Select bit

1 = Idle state for clock (CK) is a high level

0 = Idle state for clock (CK) is a low level

所以不多解释。

(2)CKE是Clock Edge Select,就是相位=CPHA:

CKE: SPI Clock Edge Select bit

1 = Transmit occurs on transition from active to Idle clock state

0 = Transmit occurs on transition from Idle to active clock state

意思是

1 =(数据)传输发生在时钟从有效状态转到空闲状态的那一时刻

0 =(数据)传输发生在时钟从空闲状态转到有效状态的那一时刻

其中,数据传输的时刻,即图中标出的“数据transmit传输的时刻”,很明显,该时刻是一个时钟和下一个时钟之间交界的地方,对应的不论是上升沿还是下降沿,都与我们前面提到的CPHA=数据采样的时刻,的边沿方向所相反。

所以,此处的CKE,正好与CPHA相反。

所以,CKP和CKE所对应的取值的含义为:

When CKP = 0:

CKE=1 => Data transmitted on rising edge of SCK

CKE=0 => Data transmitted on falling edge of SCK

When CKP = 1:

CKE=1 => Data transmitted on falling edge of SCK

CKE=0 => Data transmitted on rising edge of SCK

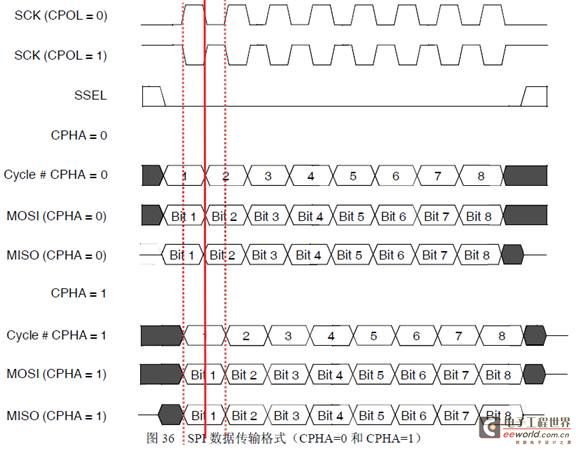

下面再列出其他一些地方找到的,常见的SPI的四种模式的时序图,供参考:

【如何看懂和记忆CPOL和CPHA】

所以,关于在其他地方介绍的,看似多么复杂难懂难记忆的CPOL和CPHA,其实经过上面解释,就肯容易看懂了:

去看时序图,如果起始的始终SCLK的电平是0,那么CPOL=0,如果是1,那么CPOL=1,

然后看数据采样时刻,即时序图数据线上的数据那个矩形区域的中间所对应的位置,对应到上面SCLK时钟的位置,对应着是第一个边沿或是第二个边沿,即CPHA是0或1。(对应的是上升沿还是还是下降沿,要根据对应的CPOL的值,才能确定)。

评论