PCI总线的存储器读写总线事务

(1)

(2)

(3)

(4)

(5)

以上过程仅是PCI设备向存储器读写数据的一个简单流程。如果考虑处理器中的Cache,这些存储器读写过程较为复杂。

PCI总线还允许PCI设备之间进行数据传递,PCI设备间的数据交换较为简单。在实际应用中,PCI设备间的数据交换并不常见。下文以图1‑1为例,简要介绍PCI设备11将数据写入PCI设备01的过程;请读者自行考虑PCI设备11从PCI设备01读取数据的过程。

(1)

(2)

(3)

1.3.5Delayed传送方式

如上文所述,如果处理器使用Non-Posted总线周期对PCI设备进行读操作,或者PCI设备使用Non-Posted总线事务对存储器进行读操作时,如果数据没有到达目的地,那么在这个读操作路径上的所有PCI总线都不能被释放,这将严重影响PCI总线的使用效率。

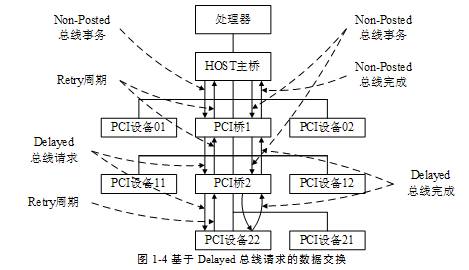

为此PCI桥需要对Non-Posted总线事务进行优化处理,并使用Delayed总线事务处理这些Non-Posted总线事务,PCI总线规定只有Non-Posted总线事务可以使用Delayed总线事务。PCI总线的Delay总线事务由Delay读写请求和Delay读写完成总线事务组成,当Delay读写请求到达目的地后,将被转换为Delay读写完成总线事务。基于Delay总线请求的数据交换如图1‑4所示。

(1)

(2)

(3)

(4)

(5)

(6)

(7)

由以上分析可知,Delayed总线周期由Delayed总线请求和Delayed总线完成两部分组成。下文将Delayed读请求总线事务简称为DRR(Delayed Read Request),Delayed读完成总线事务简称为DRC(Delayed Read Completion);而将Delayed写请求总线事务简称为DWR(Delayed Write Request),Delayed写完成总线事务简称为DWC(Delayed Write Completion)。

PCI总线使用Delayed总线事务,在一定程度上可以提高PCI总线的利用率。因为在进行Non-Posted总线事务时,Non-Posted请求在通过PCI桥之后,可以暂时释放PCI总线,但是采用这种方式,HOST/PCI桥将会择时进行重试操作。在许多情况下,使用Delayed总线事务,并不能取得理想的效果,因为过多的重试周期也将大量消耗PCI总线的带宽。

为了进一步提高Non-Posted总线事务的执行效率,PCI-X总线将PCI总线使用的Delayed总线事务,升级为Split总线事务。采用Split总线事务可以有效解决HOST/PCI桥的这些重试操作。Split总线事务的基本思想是发送端首先将Non-Posted总线请求发送给接收端,然后再由接收端主动地将数据传递给发送端。

除了PCI-X总线可以使用Split总线事务进行数据传送之外,有些处理器,如x86和PowerPC处理器的FSB(Front Side Bus)总线也支持这种Split总线事务,因此这些HOST主桥也可以发起这种Split总线事务。在PCIe总线中,Non-Posted数据传送都使用Split总线事务完成,而不再使用Delayed总线事务。本章将在第1.5.1节简要介绍Split总线事务和PCI-X总线对PCI总线的一些功能上的增强。

[1]如果是存储器、I/O读或者配置读总线事务,这个回应包含数据;如果是I/O写或者配置写,这个回应不包含数据。

评论