片上总线Wishbone 学习(九)总线周期之单次写操作

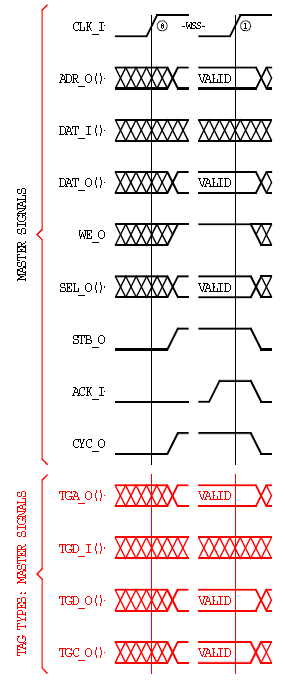

异步周期结束方式

图1

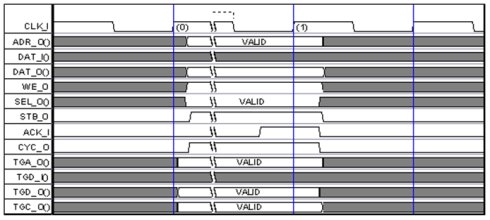

同步周期结束方式

图2

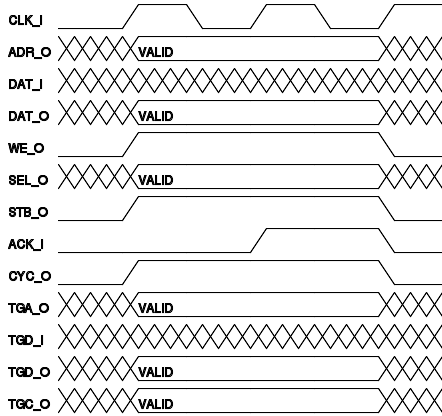

在时钟上升沿0:

- Master在[ADR_O()]和[TGA_O()]发出有效的地址

- Master在[DAT_O()]和[TGD_O()]发出数据

- Master发出[WE_O],表明是一个写周期

- Master发出有效数据选择信号[SEL_O()]表明哪些数据是有效的

- Master发出[CYC_O]和[TGC_O()]表明总线周期的开始

- Master发出[STB_O]表明操作的开始

在时钟上升沿1:

- Slave检测到主设备发起的操作,准备发出[ACK_I]

- Slave准备锁存[DAT_O]和[TGD_O()]

- Slave发出[ACK_I]应答[STB_O],表明数据有效,可以读取数据了

- Master发现[ACK_I],准备结束总线周期

注意:Slave可以在发出[ACK_I]前插入等待周期(-WSS-),以控制传速度。可以插入任意多个等待周期。

在时钟上升沿2:

- Slave锁存[DAT_I]和[TGD_I()]

- Master拉低[STB_O]和[CYC_O],表明总线周期的结束

- Slave发现Master拉低[STB_O],也将[ACK_I]拉低

评论