ARM核920T性能优化之MMU

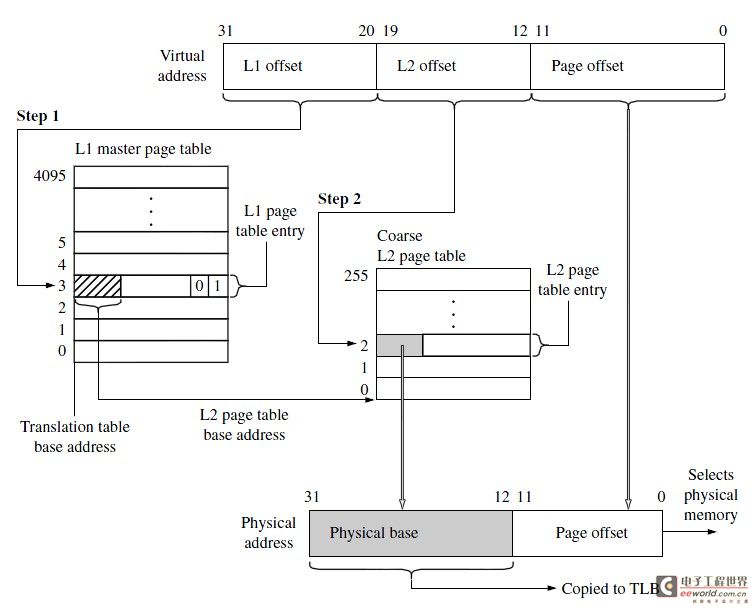

2步页表搜索:

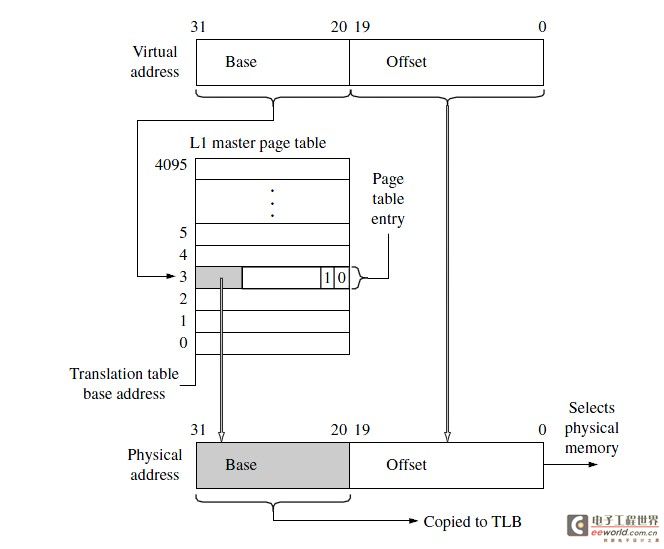

如果MMU搜索的是大小为1KB,4KB,16KB或64KB的页,则页表搜索须执行2步才能找到地址转换数据。

四.域和访问权限

有两种不同的控制用来管理一个任务的存储器访问权限,:域(domain)用于主控制(primay control),页表中的访问权限用于次控制(secondary control)。有16种不同的域可以分配给虚存的1MB段,并通过设置L1主页表项(PTE)中的域的有关位(位域)来分配给一个段。

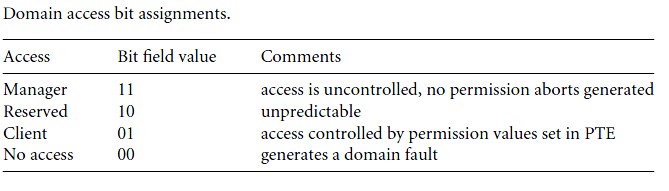

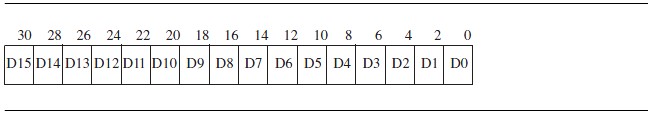

当一个域分配给了一个段时,它必须遵守分配给这个域的访问权限。域的访问权限在CP15:c3寄存器中分配,它控制处理器核访问虚存段的能力。16个可用的域,每个域使用CP15:c3寄存器的2位来定义访问权限,域访问位取值及对应的意义如下表所列:

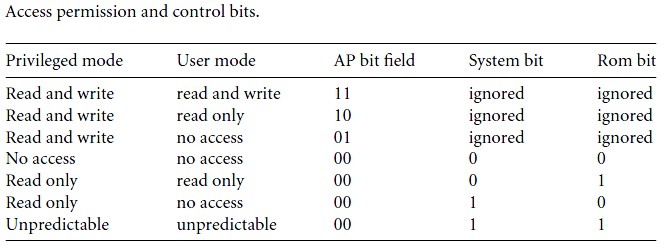

基于页表的访问权限。页表项中的AP位决定该页的访问权限。“AP”,“ap3”,“ap2”,“ap1”,“ap0”结合CP15寄存器C1的R/S位,决定如何进行访问权限检查。段描述符中的“AP”

控制整个段(1MB)的访问权限;大页描述符中的每个“apx”(x为0~3)控制一个大页(64KB)中1/4内存的访问权限,即“ap3”对应大页高端的16KB,“ap0”对应大页低端的16KB;小页描述符与大页描述符相似,每个“apx”控制一个小页(4KB)的1/4内存的访问权限。极小页中的“ap”就控制整个极小页1KB的访问权限。

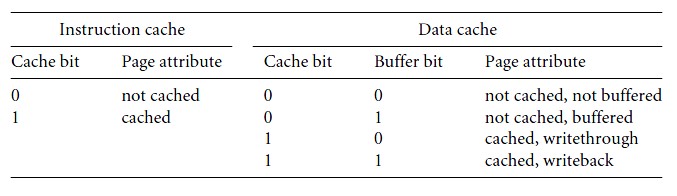

五.Cache和写缓冲

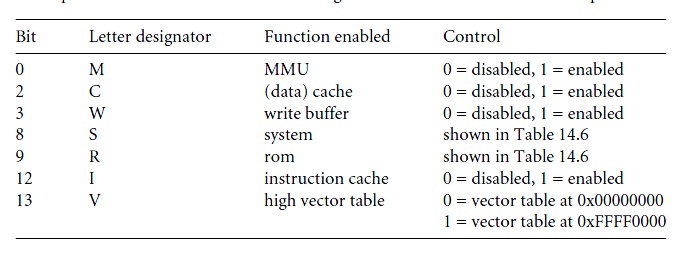

六.CP15:c1控制寄存器

七.快速上下文切换扩展

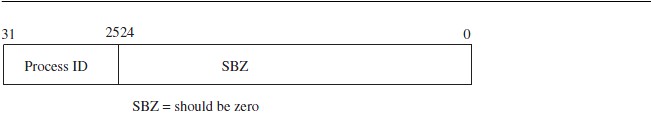

快速上下文切换扩展FCSE(Fast Context Switch Extension),是MMU中的一个附加硬件,用于提高ARM嵌入式系统的系统性能。FCSE使得多个独立的任务可以运行在一个固定的重叠存储空间中,而上下文切换时又不需要清理或清除cache,或TLB。如果没有FCSE,则从一个任务切换到另一个任务需要改变虚拟存储映射。如果涉及两个有重叠地址的任务,则保存在cache和TLB中的信息将变为无效,这样系统就必须清除cache和TLB中的无效数据。清除这些模块的过程使任务切换增加了很多时间,因为内核不仅要清除cache和TLB中的无效数据,还要从主存中装载新的数据到cache和TLB。使用FCSE,虚拟存储管理增加了一次地址转换。FCSE在虚拟地址到达cache和TLB前,使用一个特殊的,包含进程ID值的重定位寄存器来修改虚拟地址。把修改之前的虚存地址称为VA(Virtual Address),把第一次转换之后的地址称为修改后虚地址MVA(Modified Virtual Address)。这样,任务间的切换就不用涉及到改变页表,只需简单的将新任务的进程ID写到位于CP15的FCSE进程ID寄存器。为了利用FCSE,编译链接所有的任务,使他们都运行在虚存的第一个32MB块空间,为每个任务分配一个进程ID;然后通过下边的公式,将每个任务放置在修改后虚存的不同32MB分区中:

MVA = VA +(0x2000000 * 进程ID)

下图是一个快速上下文切换扩展的例子:在一个3任务的多任务环境中,切换前任务1运行,切换后任务2运行。

评论