MSP430(F5529)学习笔记——UCS配置详解

(3)将SMCLK和MCLK配置XT2

将SMCLK和MCLK配置为XT2跟配置为XT1的过程基本相同,唯一不同的是,在配置SMCLK和MCLK为XT2之前,需要将ACLK和REFCLK的时钟源,因为ACLK和REFCLK的默认时钟源是XT1,而我们这里并没有配置启动XT1CLK,所以会产生XT1时钟错误,即XT1LFFG,因此,我们先将ACLK和REFCLK配置为芯片自带的时钟(REFOCLK或VLOCLK)或者即将启动的时钟(XT2),此外,XT2配置时不需要配置电容,故将SMCLK和MCLK配置为XT2的代码如下:

[cpp]view plaincopy

- #include

- voidmain(void){

- WDTCTL=WDTPW+WDTHOLD;

- P1SEL|=BIT0;

- P1DIR|=BIT0;//测量ACLK用

- P2SEL|=BIT2;

- P2DIR|=BIT2;//测量SMCLK用

- P7SEL|=BIT7;

- P7DIR|=BIT7;//测量MCLK用

- P5SEL|=BIT2|BIT3;//将IO配置为XT2功能

- UCSCTL6&=~XT2OFF;//使能XT2

- UCSCTL4=UCSCTL4&(~(SELA_7))|SELA_1;//先将ACLK配置为VLOCLK

- UCSCTL3|=SELREF_2;//将REFCLK配置为REFCLK

- while(SFRIFG1&OFIFG){

- UCSCTL7&=~(XT2OFFG+XT1LFOFFG+DCOFFG);//清除三类时钟标志位

- //这里需要清除三种标志位,因为任何一种

- //标志位都会将OFIFG置位

- SFRIFG1&=~OFIFG;//清除时钟错误标志位

- }

- UCSCTL4=UCSCTL4&(~(SELS_7|SELM_7))|SELS_5|SELM_5;//将SMCLK和MCLK时钟源配置为XT2

- while(1);

- }

DCO模块详解

DCO模块在MSP430F5XX系列芯片中非常重要,因为从MSP430F4XX开始,MSP430引用了FLL模块,FLL即锁相环,可以通过倍频的方式提高系统时钟频率,进而提高系统的运行速度。

DCO模块运行需要参考时钟REFCLK,REFCLK可以来自REFOCLK、XT1CLK和XT2CLK,通过UCSCTL3的SELREF选择,默认使用的XT1CLK,但如果XT1CLK不可用则使用REFOCLK。

DCO模块有两个输出时钟信号,级DCOCLK和DCOCLKDIV,其中,倍频计算公式如下:

[cpp]view plaincopy

- DCOCLK=D*(N+1)*(REFCLK/n)

- DCOCLKDIV=(N+1)*(REFCLK/n)

其中:

n即REFCLK输入时钟分频,可以通过UCSCTL3中的FLLCLKDIV设定,默认为0,也就是不分频;

D可以通过UCSCTL2中的FLLD来设定,默认为1,也就是2分频;

N可以通过UCSCTL2中的FLLN来设定,默认值为32。

所以,系统上电后如果不做任何设置,DCOCLK的实际值为2097152,DCOCLKDIV的实际值为1048576。

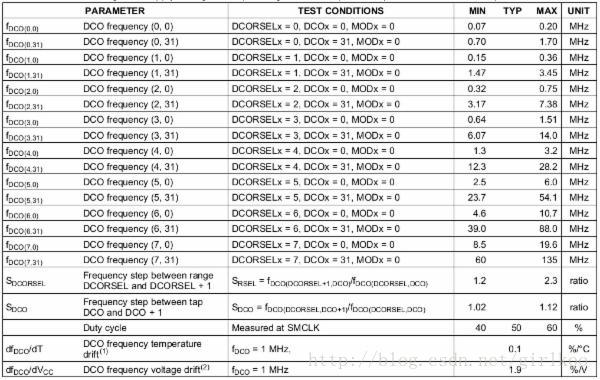

另外,配置芯片工作频率还需要配置DCORSEL和DCOx,DCORSEL和DCOx的具体作用如下:

DCORSEL位于UCSCTL1控制寄存器中的4到6位,共3位,将DCO分为8个频率段。

DCOx位于UCSCTL0中的8到12位,共5位,将DCORSEL选择的频率段分为32个频率阶,每阶比前一阶高出约8%,该寄存器系统可以自动调整,通常配置为0。

DCORSEL和DCOx值的具体作用可以参考MSP430F5529的数据手册,阅读该手册相关部分可以找到如下表格:

本文引用地址:https://www.eepw.com.cn/article/201611/322859.htm

可以见,DCORESL的频率调节范围大致如下:

[cpp]view plaincopy

- DCORSEL=0的调节范围约为0.20~0.70MHZ;

- DCORSEL=1的调节范围约为0.36~1.47MHZ;

- DCORSEL=2的调节范围约为0.75~3.17MHZ;

- DCORSEL=3的调节范围约为1.51~6.07MHZ;

- DCORSEL=4的调节范围约为3.2~12.3MHZ;

- DCORSEL=5的调节范围约为6.0~23.7MHZ;

- DCORSEL=6的调节范围约为10.7~39.7MHZ;

- DCORSEL=7的调节范围约为19.6~60MHZ。

评论