MSP430F5529 番外(二)纠正XT1配置错误

ACLK = SMCLK = MCLK =XT1 =32768

本文引用地址:https://www.eepw.com.cn/article/201611/322795.htmint main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timer

P1DIR |= BIT0; // ACLK set out to pins

P1SEL |= BIT0;

P2DIR |= BIT2; // SMCLK set out to pins

P2SEL |= BIT2;

P7DIR |= BIT7; // MCLK set out to pins

P7SEL |= BIT7;

P5SEL |= BIT4+BIT5; // Select XT1

UCSCTL6 &= ~(XT1OFF); // XT1 On

UCSCTL6 |= XCAP_3; // Internal load cap

UCSCTL3 = 0; // FLL Reference Clock = XT1

// Loop until XT1,XT2 & DCO stabilizes - In this case loop until XT1 and DCo settle

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

UCSCTL6 &= ~(XT1DRIVE_3); // Xtal is now stable, reduce drive strength

UCSCTL4 = SELA_0 + SELS_0 + SELM_0; // SMCLK = MCLK =ACLK = LFTX1

}

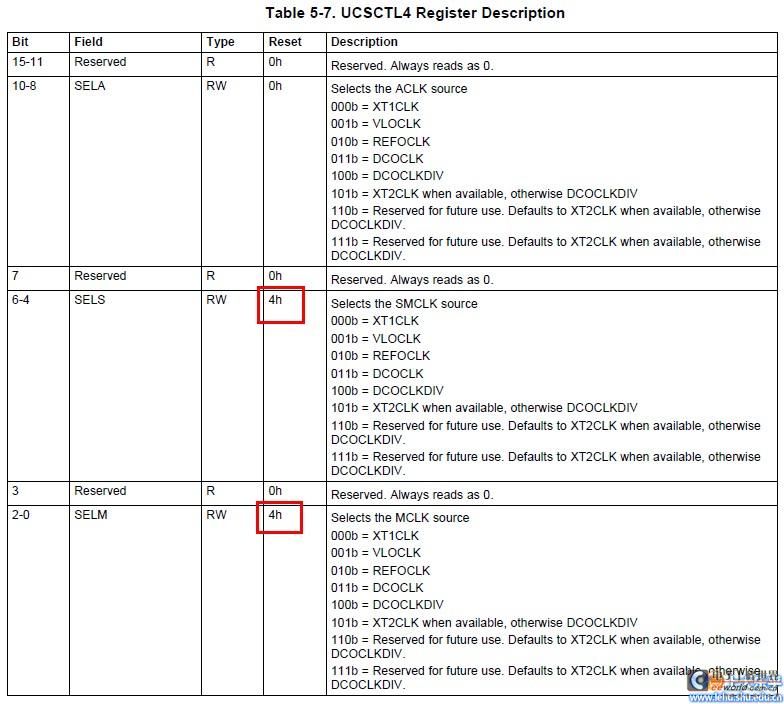

注意划红线的语句,要用等号赋值。因为默认 SELS 和SELM的值是不为0的,所以用或赋值的话会出错。

默认值请看下表:

评论