单片机以太网控制芯片W7100A数据手册(二)

注意:

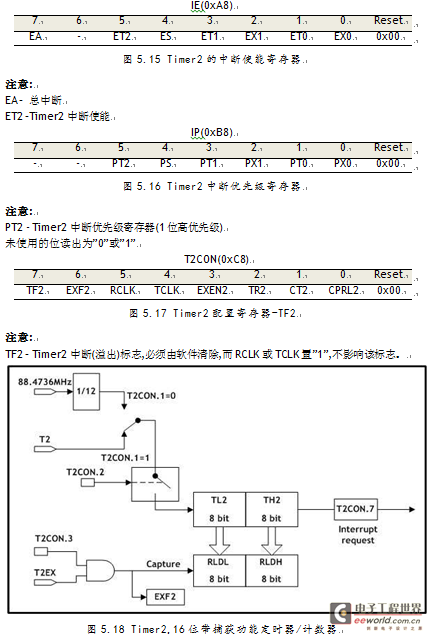

EXF2 – 当EXEN2=1时,表示T2EX输入有下降沿的信号。必须由软件清零。

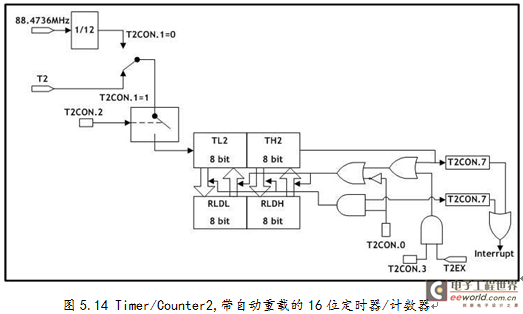

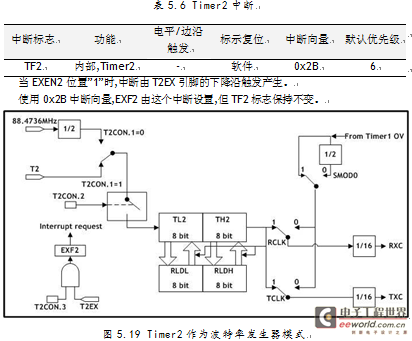

RCLK – 接收时钟使能位

0: Timer1的溢出脉冲作为UART的接收器时钟

1: Timer2的溢出脉冲作为UART的接收器时钟

TCLK – 发送时钟使能位

0: Timer1的溢出脉冲作为UART的发送器时钟

1: Timer2的溢出脉冲作为UART的发送器时钟

EXEN2 – T2EX引脚功能允许位

0: 忽略T2EX事件

1: T2EX引脚的下降沿允许捕获或重装载

TR2 –启动/停止Timer2

0:停止

1:启动

CT2 – 定时器/计数器选择

0:内部时钟定时器

1:外部事件计数器,时钟源由T2引脚输入

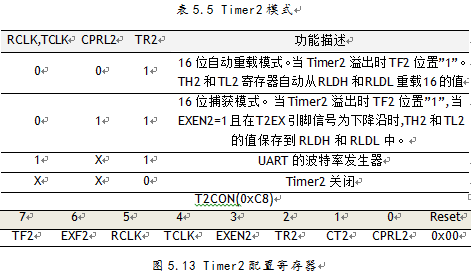

CPRL2 – 捕获/重载选择

0:当Timer2溢出,或在EXEX2=1且T2EX引脚出现下降沿输入时,产生自动重载。当RCLK或TCLK置位,忽略该位,并在Timer2溢出时自动重载。

1: 当EXEN2=1时,T2EX引脚出现下降沿输入时激活捕获功能。

5.2.2

Timer2的中断如下。中断可以由IE寄存器的对应位触发,由IP寄存器的对应位配置其优先级。

所有产生中断的位可以由软件设置或清除。与硬件产生的结果相同,也就是说中断可以由软件产生或清除。

评论