STM8 时钟

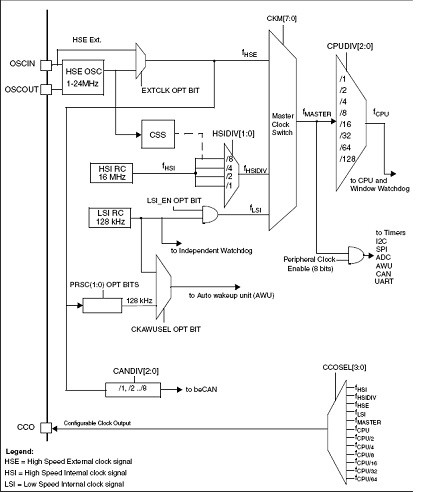

主时钟源:

1-24MHz高速外部晶体振荡器(HSE)

最大24MHz高速外部时钟信号(HSE user-ext)

16MHz高速内部RC振荡器(HSI)

128KHz低速内部RC(LSI)

各个时钟源可单独打开或关闭,从而优化功耗。

(一)HSE

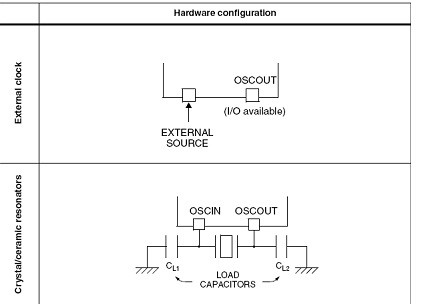

高速外部时钟信号可由下面两个时钟源产生:

HSE外部晶体/陶瓷谐振器

HSE用户外部有源时钟

为了最大限度减小输出失真和减小启动的稳定时间,谐振器和负载电容应尽可能得靠近振荡器引脚。负载电容值应根据所选的振荡器进行调整。

- 外部晶体/陶瓷谐振器(HSE晶体)

外部1至24MHz的振荡器其优点在于能够产生精确的占空比为50%的主时钟信号。

硬件连接如图14所示。更多详情请参见数据手册电特性章节。振荡器在启动时的输出时钟信号是不稳定的,默认情况下,在时钟信号被使用之前会插入2048个振荡器周期的延迟。用户可通过设置选项字节HSECNT来缩短稳定时间,请参见数据手册的选项字节章节。外部时钟寄存器CLK_ECKR中的标志位HSERDY用以指示高速外部振荡器是否稳定。启动时,HSE时钟信号将不会生效直至此标志位被硬件置位。

HSE晶体可通过设置外部时钟寄存器CLK_ECKR中的HSEEN位来打开或关闭。 - 外部时钟源(HSE用户外部时钟)

这种模式下,必须由用户提供一个外部时钟,此时钟的最高频率可为24MHz。用户可通过编程选项位EXTCLK选择此模式。详情请参见数据手册的选项字节章节。此时,占空比约50%的外部时钟信号(方波,正弦波,三角波)用以驱动OSCIN引脚,而OSCOUT引脚可做为通用输入/输出管脚使用。

(二)HSI

HSI信号由内部16MHz RC振荡器与一个可编程分频器(分频因子从1至8)产生。分频因子由寄存器CLK_CKDIVR决定。

注意:启动时,主时钟源默认为HSI RC时钟的8分频,即fHSI/8

HSI RC可以提供一个低成本的16MHz时钟源(无需外部器件),其占空比为50%。HSI启动速度比HSE晶体振荡器快,但是其精度即使经过校准也仍然比外部晶体振荡器或陶瓷谐振器低。内部时钟寄存器CLK_ICKR中的标志位HSIRDY用以指示HSI RC是否稳定。启动时,HSI时钟信号将不会生效直至此标志位被硬件置位。HSI RC可通过设置内部时钟寄存器CLK_ICKR中的HSIEN位打开或关闭。

备份时钟源

当HSE晶体振荡器失效时,HSI/8可作为备份时钟源(辅助时钟源)使用。请参见8.6时钟安全系统(CSS)。

快速启动特性

如果寄存器CLK_ICKR中的FHWU位被置1,则MCU从停机(Halt)模式或活跃停机(Active Halt)模式唤醒时,HSI将自动被设为主时钟源。

校准

每个产品在出厂时均已经ST校准。

复位后,出厂校准值将被自动加载至内部校准寄存器。

如果实际应用中电压或温度偏差较大,将会影响RC振荡器的速度。用户可使用HSI时钟校准寄存器(CLK_HSITRIMR)修正HSI的时钟频率。此寄存器中有3或4位用以存放一个附加的修正值,并与内部HSI校准寄存器的值相加来对时钟进行校正。

(三)LSI

128KHz的LSI RC时钟是一个低功耗,低成本的可选主时钟源,也可在停机(Halt)模式下作为维持独立看门狗和自动唤醒单元(AWU)运行的低功耗时钟源。LSI可通过设置内部时钟寄存器CLK_ICKR中的LSIEN位打开或关闭。

内部时钟寄存器CLK_ICKR中的标志位LSIRDY用以指示LSI是否稳定。启动时,LSI时钟信号将

不会生效直至此标志位被硬件置位。

同HIS一样,LSI出厂时已经校准。但是,不可能再执行进一步的校准。

注意:当独立看门狗使用LSI为时钟源时,为了保证CPU在系统出错时不与独立看门狗使用同一个时钟,

当选项字节位LSI_EN为0时,LSI不能做为主时钟。请参见STM8数据手册中的选项字节章节。

时钟切换

时钟切换功能为STM8用户提供了一种易用、快速、安全的从一个时钟源切换到另一个时钟源的途径。

系统启动

为使STM8系统快速启动,复位后时钟控制器自动使用HSI的8分频(HSI/8)做为主时钟。其原因为HSI的稳定时间短,而8分频可保证系统在较差的VDD条件下安全启动。一旦主时钟源稳定,用户程序可将主时钟切换到另外的时钟源。

主时钟切换的过程

用户可选择下面两种方式切换时钟源:

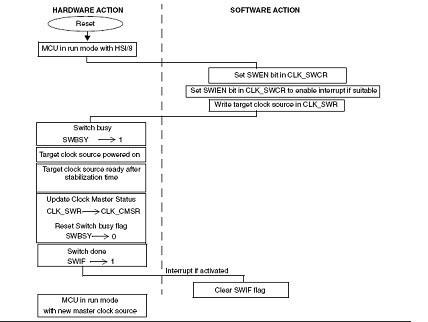

自动切换

自动切换使用户可使用最少的指令完成时钟源的切换。应用软件可继续其它操作而不用考虑切换事件所占的确切时间。

1.设置切换控制寄存器(CLK_SWCR)中的位SWEN,使能切换机制。

2.向主时钟切换寄存器(CLK_SWR)写入一个8位的值,用以选择目标时钟源。寄存器CLK_SWCR中的SWBSY被硬件置位,目标源振荡器启动。原时钟源依然被用于驱动内核和外设。

一旦目标时钟源稳定,寄存器CLK_SWR中的值将被复制到主时钟状态寄存器(CLK_CMSR)中去。

此时,SWBSY位被清除,新时钟源替代旧时钟源。寄存器CLK_SWCR中的标志位SWIF被置位,如果SWIEN为1,则会产生一个中断。

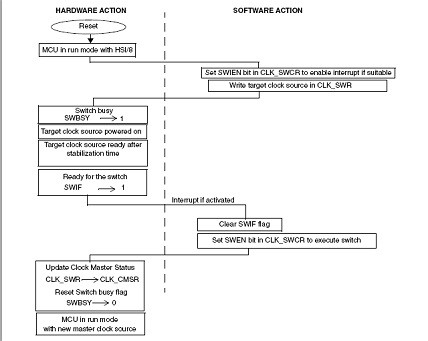

- 手动切换

手动切换与自动切换不同,不能够立即切换,但它允许用户精确地控制切换事件发生的时间

1.向主时钟切换寄存器(CLK_SWR)写入一个8位的值,用以选择目标时钟源。寄存器CLK_SWCR中的SWBSY被硬件置位,目标源振荡器启动。原时钟源依然被用于驱动内核和外设。

2.用户软件需等待至目标时钟源稳定。寄存器CLK_SWCR中的标志位SWIF用以指示目标时钟源是否已稳定,如果SWIEN为1,则会产生一个中断。

3.最后,由用户软件在所选的时间点,设置寄存器CLK_SWCR中的位SWEN,执行切换。无论是手动切换还是自动切换,如果原时钟源仍然在被其他模块使用(如LSI在被独立看门狗使用),则原时钟源将不会被自动关闭。配置内部时钟寄存器CLK_ICKR和外部时钟寄存器

CLK_ECKR中的相应位,可关闭原时钟源。如果由于某种原因时钟切换没有成功,软件可通过清除标志位SWBSY以复位当前的切换操作,使寄存器CLK_SWR恢复原值(原时钟源)。

外设时钟门控

关闭未使用外设的时钟可使STM8降低功耗。外设的时钟门控(PCG)模式使用户可在运行模式下随时打开或关闭fMASTER与下列外设的连接:

- ADC

- I2C

- AWU(寄存器时钟,而非计数器时钟)

- SPI

- TIM[4:1]

- UART

- CAN(寄存器时钟,而非CAN时钟)

STM8系统复位后,所有外设时钟均处于开的状态。用户可通过清除CLK_PCKENR1或CLK_PCKENR2中的PCKEN位来关闭相应的外设时钟。但是在关闭外设的时钟前,用户必须设置相应的位禁用该外设。

为了使能一个外设,用户必须先设置寄存器CLK_PCKENR中对应的PCKEN位,然后设置外设控制寄存器中的外设使能位。

AWU计数器是由独立于fMASTER的内部或外部时钟(LSI或HSE)驱动,因此,即使寄存器的时钟已被关掉,该外设依然可以继续运行。时钟安全系统

时钟安全系统用于监控HSE时钟源是否失效。当fMASTER使用HSE做为时钟源时,如果HSE时钟由于谐振器损坏、断开或其它原因而失效,时钟控制器将激活安全恢复机制,将fMASTER自动切换到辅助时钟源HSI/8。STM8系统将一直使用辅助时钟源,直至MCU被复位。

设置时钟安全系统寄存器CLK_CSSR中的CSSEN位,可使能STM8的时钟安全系统。为安全起见,CSS一旦使能就不能被关闭,直到下一次复位。

必须满足下面的条件,CSS方可检测HSE石英晶体的失效:

- HSE晶体开:(外部时钟寄存器CLK_ECKR中的位HSEEN=1)

- HSE振荡器被置为石英晶体(选项位EXTCLK为1)

- CSS功能开:(寄存器CLK_CSSR中CSSEN=1)

如果当前的主时钟源为HSE,当失效被检测到时,CSS将执行以下操作:- 寄存器CLK_CSSR中的CSSD位被置位,如果CSSIEN为1,则同时产生一个中断。

- CLK_CMSR,CLK_SWR,及CLK_CKDIVR中的HSIDIV[1:0]位被置为复位值(CKM[7:0]=SWI[7:0]=E1h)。HSI/8成为主时钟。

- 内部时钟寄存器CLK_ICKR中的HSIEN被置位(HSI开)。

- 外部时钟寄存器CLK_ECKR中的HSEEN被清除(HSE关)。

- AXU位被置位,用以指示辅助时钟源HSI/8被强制使用。

用户可通过软件清除CSSD位,但AXU位只能由复位清除。为了提高时钟频率,用户在清除寄存器CLK_CSSR中的CSSD位以后,可修改寄存器

CLK_CKDIVR中的HSIDIV[1:0]位。

如果失效发生时HSE不是主时钟源,STM8主时钟将不会被切换到辅助时钟源,以上操作也不会发生,仅执行下面的操作:- 外部时钟寄存器CLK_ECKR中的HSEEN被清除,HSE关闭。

- 寄存器CLK_CSSR中的位CSSD被置位,如果CSSIEN为1,则同时产生一个中断。

如果HSE不是当前主时钟源,且主时钟正在被切换至HSE,则在清除CSSD位之前,必须先清除寄存器CLK_SWCR的SWBSY位。

如果当失效被检测到时,HSE被CCOSEL选择为时钟输出模式(参见时钟输出功能(CCO)),则HSI(HSIDIV)将替代HSE,被自动强制选择为输出时钟。时钟输出CCO

可配置的时钟输出功能使STM8用户可在外部管脚CCO上输出指定的时钟。STM8S的用户可选择下面6种时钟信号之一做为CCO时钟:

- fHSE

- fHSI

- fHSIDIV

- fLSI

- fMASTER

- fCPU(可选择分频值)

注意:在所有可能的分频值下,不能保证信号的占空比全部为50%

通过配置时钟输出寄存器CLK_CCOR中域CCOSEL[3:0]可选择输出的时钟。用户需为指定的I/O引脚(参见管脚描述章节)选择期望输出的时钟。此I/O必须通过配置寄存器Px_CR1对应的位为1来设置为上拉输入或推挽输出模式。

一旦可配置时钟输出寄存器CLK_CCOR的位CCOEN=1,就开始输出所选定的时钟信号。如果CCOBSY为1,则表明可配置时钟输出系统正在工作。只要CCOBSY为1,CCOSEL位就会被写保护。

如果需要,CCO可自动激活目标振荡器。当所选时钟就绪时,CCORDY被置位。STM8用户可通过清除CCOEN位来禁用时钟输出功能。CCOBSY位和CCORDY位都将保持为1直到禁用操作结束。从清除CCOEN位到这两个标志位被复位之间的时间可能会很长,例如当所选的输出时钟相对于fCPU频率很低时。

时钟中断

当下列事件发生时,时钟控制器可产生中断:

- 主时钟源切换事件

- CSS事件

这两个中断均可被独立屏蔽。

评论