高隔离度、硅SPDT、非反射开关,9 kHz至13.0 GHz

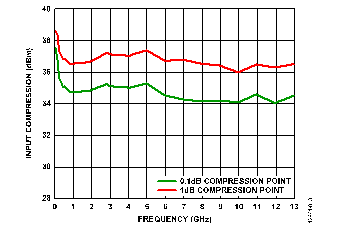

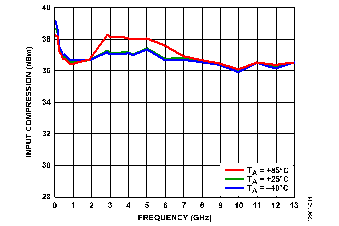

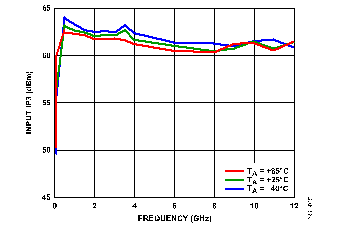

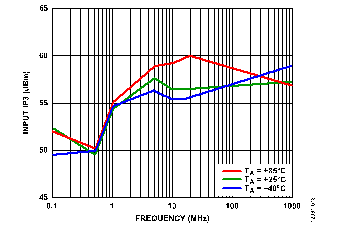

输入压缩点和输入三阶交调截点

本文引用地址:https://www.eepw.com.cn/article/201608/295978.htm

图13. 0.1 dB和1 dB压缩点与频率的关系

图14. 不同温度下1 dB输入压缩点与频率的关系

图15. 不同温度下输入三阶交调截点(IIP3)与频率的关系

图16. 0.1 dB和1 dB输入压缩点与频率的关系(低频细节)

图17. 不同温度下1 dB输入压缩点与频率的关系(低频细节)

图18. 不同温度下输入三阶交调截点(IIP3)与频率的关系(低频细节)

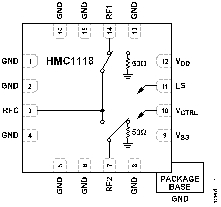

工作原理

HMC1118要求将一个正电源电压施加于VDD引脚,将一个副电源电压施加于VSS引脚。 建议在电源线路上连接旁路电容,以将RF耦合降至最低。 将一个正电源电压施加于VDD引脚而将负电压输入引脚(VSS)接地时,HMC1118也能工作,不过输入功率压缩和三阶交调截点的性能可能会降低。

HMC1118通过施加于VCTRL引脚和LS引脚的两个数字控制电压进行控制。 建议在这些数字信号线上连接一个小值旁路电容以改善RF信号隔离性能。

HMC1118内部匹配RF输入端口(RFC)和RF输出端口(RF1和RF2)的50 Ω电阻,因而不需要外部匹配元件。 RF1和RF2引脚为直流耦合,若RF电位不等于0 V共模电压,则RF路径需要隔直电容。 设计为双向,输入和输出可以互换。

理想的通电序列如下:

1. GND上电。

2. VDD和VSS上电。 相对顺序不重要。

3. 数字控制输入上电。 逻辑控制输入的相对顺序不重要。 数字控制输入先于VDD电源上电可能会导致意外正偏并损害内部ESD保护结构。

4. RF输入上电。

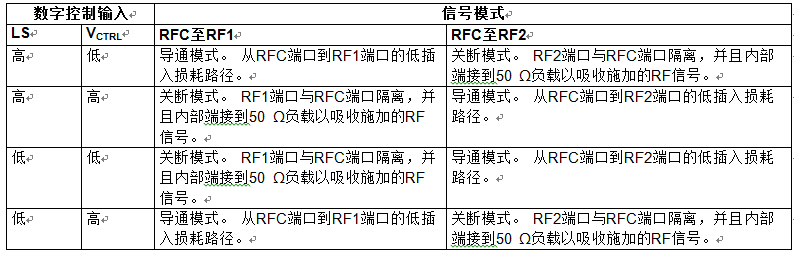

逻辑选择(LS)用于定义RF路径选择的控制输入逻辑序列。 若LS引脚设为逻辑高电平,则当VCTRL为逻辑低电平时,RFC至RF1路径导通;当VCTRL为逻辑高电平时,RFC至RF2路径导通。 若LS设为逻辑低电平,则当VCTRL为逻辑高电平时,RFC至RF1路径导通;当VCTRL为逻辑低电平时,RFC至RF2路径导通。

根据施加于LS和VCTRL引脚的逻辑电平,一个RF输出端口(例如RF1)设置为导通模式,插入损耗路径将输入提供给输出。 另一个RF输出端口(例如RF2)设置为关断模式,输出与输入隔离。 当RF输出端口(RF1或RF2)处于隔离模式时,将其内部端接到50 Ω电阻,端口吸收施加的RF信号(参见表7)。

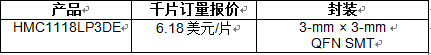

表7. 开关工作模式

应用信息

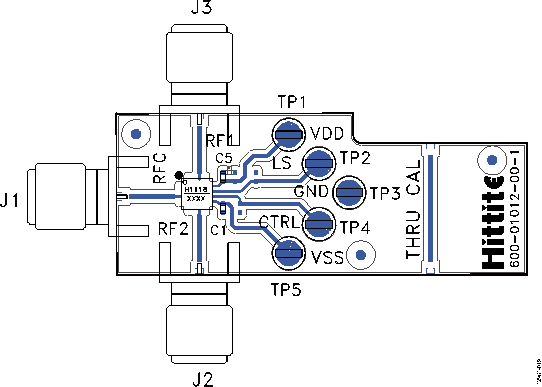

评估PCB

利用适当的RF电路设计技术产生本应用所用的评估PCB。 RF端口的信号线必须具有50 Ω阻抗,封装接地引脚和背面接地金属块必须直接连接到接地层,类似图19中所示。 图19所示评估板可向ADI公司申请获得。

图19. EV1HMC1118LP3D评估PCB

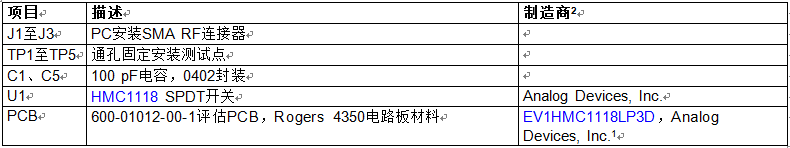

表8. EV1HMC1118LP3D评估板物料清单1

1 订购完整评估PCB时请提供此号码。

2“制造商”栏中的空白单元表示相应元件可由用户选择。

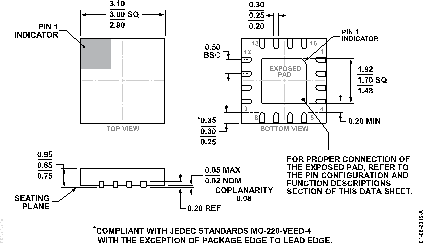

外形尺寸

图20. 16引脚引线框芯片级封装[LFCSP_WQ]

3 mm × 3 mm,超薄体

(CP-16-38)

图示尺寸单位:mm

评论