基于ADμC7020的高速误码测试仪

2.2 硬件设计

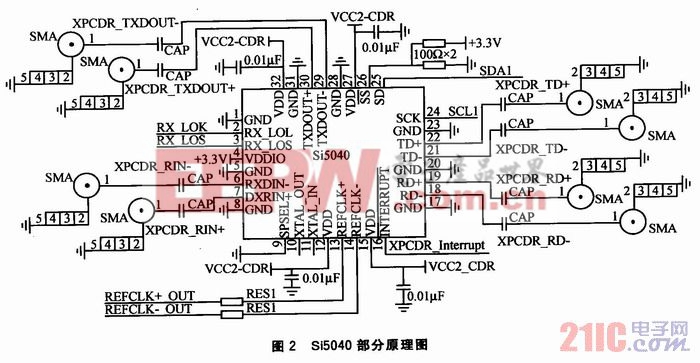

本文硬件设计仅列出Si5040和ADμC7020两部分的原理图。

2.2.1 Si5040

Si5040的PINl3和PINl4是参考时钟输入引脚。在此设计应用中使用Silicon Laboratories公司的SI534四频晶体振荡器(XO),其工作频率范围10 MHz~1.4 GHz,RMS抖动低于O.3 ps,可提供高线性度的控制电压及宽范围的电压增益选择,并可以支持PECL、LVDS、CMOS和CML各种电平形式的输出。

Si5040的通信接口支持I2C和类SPI模式。通过SPSEL(PIN9)来选择使用接口的类型。当SPSEL置低电平时,使用I2C接口类型,PIN25(ser-ial data line,SD)and PIN24(serial clock input,SCK)作为I2C总线的SDA和SCL。当SPSEL置高电平时,使用类SPI接口类型。

Si5040在发端和收端都有可编程的码型模式生成器和检查器。发端信道使用TxtpSel寄存器,可配置成PRBS7、PRBS31或者64位用户自定义码型。

Interrupt、RX_LOL和Rx_LOS反映Si5040的工作状态。由ADμC7020的I/O口来采样其电平逻辑,由此反映Si5040的工作状态。

TD+、TD-、TXDOUT+、TXDOUT-和RD+、RD-、RXDIN+、RXDIN-接入SMA头,信号为差分CML信号。

Si5040原理图如图2所示。本文引用地址:https://www.eepw.com.cn/article/195192.htm

2.2.2 ADμC7020

使用JTAG仿真调试ADμC7020,其引脚为TMS、TDI、TCK、TD0、TRST。

使用ADμC7020的两个I2C接口。P1.1和P1.2构成I2C总线O,ADμC7020作为I2C从机。上位机PC作为I2C主机。P1.3和P1.4构成I2总线1,ADμC7020作为I2C主机,Si5040作为I2C从机。

P0.6、P0.4和P0.5引脚作为输入脚测试Si5040的状态RX LOS、RX LOK和Interrupt。

P1.4、P1.5、P1.6、P1.7和P4.2引脚控制测试待测XFP模块的各种状态。

ADC0、ADC1和ADC2测量误码测试系统中有关电压值+5 V、+3.3 V和+1.8 V的各电压通道上的总电流值。

ADC3、ADC4和ADC12测量误码测试系统中XFP模块的电压值+5 V、+3.3 V和+1.8 V。

跳线接地时即P0.0接地,同时Flash 0x14地址的内容为0xFFFFFFFF时,在两个条件同时满足时,在ADμC7020复位时可自动进入Bootlo-ader程序(即在系统中编程ISP),这样可以不使用JTAG仿真器,以方便误码测试仪的ADμC7020的Firmware在线升级换代。

ADμC7020部分原理图如图3所示。

评论