一种用于高精度ADC片上测试的信号发生器

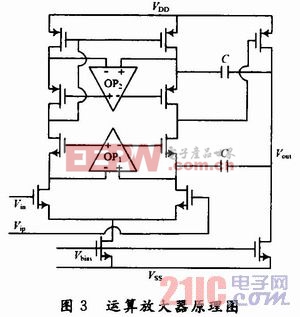

本文中运算放大器采用两级结构,如图3所示。其中:输入级采用带增益自举电路的套筒式共源共栅结构,包括主运放和辅助运放。主运放采用NMOS输入的套筒式共源共栅结构,具有高增益、低功耗以及良好的频率特性。辅助运放OP1,OP2分别为采用PMOS输入和NMOS输入的折叠式共源共栅全差分结构,进一步提高运放增益。第二级采用共源结构来改善套筒式共源共栅结构输出摆幅小的缺点,同时也能一定程度上提高运算放大器的开环增益。由于级数增加也会引入新的零极点,从而会影响运放的稳定性。所以,必须加入补偿电容C,使相位裕度满足要求。本文引用地址:https://www.eepw.com.cn/article/195109.htm

由Spectre仿真所得的运算放大器的交流幅频、相频特性如图4所示。表1总结了运算放大器的基本性能参数。

3.2 迟滞比较器设计

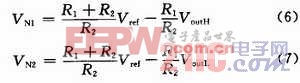

迟滞比较器的迟滞特性是比较器中引入正反馈的结果。迟滞比较器有两个输入阈值,当输入电压经过其中一个阈值时输出电压会改变,同时输入阈值会跳变到另一个值。要再次改变输出,输入必须到达跳变之后的阈值,在输出改变的同时,阈值又会跳变回原来的值。本文所采用的迟滞比较器电路及输入-输出特性曲线如图5所示。

两个输入阈值分别为:

迟滞比较器中的比较器电路采用两级开环运放实现,由于比较器后级是一个2 mΩ的电阻,所以必须使比较器输出级电阻足够低,以防止由于电阻分压而导致比较器输出电压达不到电源电压以及地电压。因此,在两级开环运放之后增加了一个大宽长比的反相器链以获得较低的输出电阻,如图6所示。

评论