多种触发功能的可编程高速数据采集模块

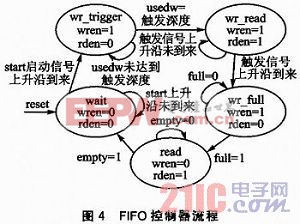

1.3 FIFO读写数据控制

FIFO存储器的读写是用状态机来实现的。5个状态分别为wait、wr_trigger、wr_read、wr_full、read。FIFO控制器流程如图4所示。模块开始进入wait状态等待启动信号start上升沿,如果start上升沿到来模块转到wr_trigger状态,否则将在wait状态一直等待;当模块进入wr_trigger状态时,FIFO开始写数据直到满足触发模式的预触发深度,此时的写时钟等于采样时钟;此后模块进入wr_read状态,FIFO开始一边读数据一边写数据,即一直保持FIFO中存储的数据是最新A/D转换数据,此时的读写时钟与采样时钟是同频的。直到触发信号上升沿的到来,否则FIFO存储器将一直读数据和写数据;当触发信号上升沿有效时,模块进入wr_full状态,FIFO存储器停止读数据,开始写数据,直到FIFO写满数据;当FIFO写满数据(full=1)以后,模块转到read状态,FIFO开始读数据并通过通信接口发送到显示控制界面进行直观的显示,直到FIFO为空empty=1,此时读时钟为显示时钟;FIFO读数据操作完毕,模块将一直停留在wait状态等待下一次采集启动信号的到来,如此反复执行。本文引用地址:https://www.eepw.com.cn/article/194706.htm

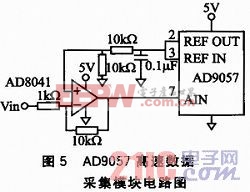

1.4 高速数据采集模块电路设计

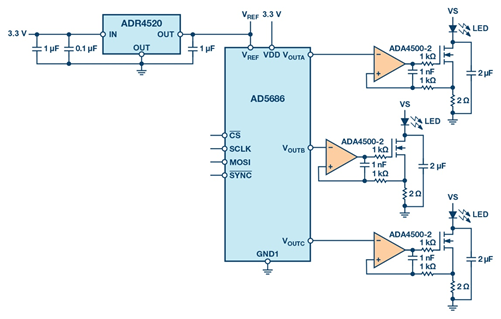

AD9057是8位的模数转换器,可以达到60 MHz的最大采样频率。设计中,模块采用50 MHz的采样频率,AD9057带有2.5V的基准电压,可以对1 V峰峰值输入模拟信号进行A/D转换。通常采用高频、宽带运放对模拟信号进行缓冲,本设计中采用AD8041作为放大器,AD9057高速数据采集模块电路图电路图如图5所示。

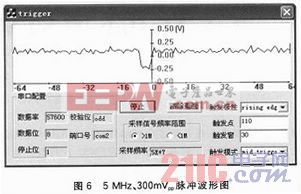

2 结论

模块可以工作在50 MHz的采样频率下,并且在模拟信号幅度偏小和有一定干扰的情况下也可以正常地工作。本次设计中采用了VC++6.0编写的显示控制界面进行模块验证。图6是数据采集模块捕捉的频率为5 MHz、300mVpp交替出现间隔为1 ms的一个脉冲波形图。

其中,触发模式选用中间触发,触发极性为上升沿,采样频率为50 MHz。由此可见,本模块的技术方案可行,具有灵活简洁的特点,可以应用在程控仪器和自适应信号采集与处理系统中。

评论