基于PLD的纳秒级脉冲发生器

1 基本原理

本文引用地址:https://www.eepw.com.cn/article/192124.htm设计采用的XILINX公司的复杂可编程逻辑器件(CPLD)几乎可适用于所有的门阵列和各种规模的数字集成电路,他以其编程方便、集成度高、速度快、价格低等特点越来越受到设计者的欢迎。选用的CPLD为XILINX公司的XC9572XL,属于XC9500系列,是目前业界速度较快的高集成度可编程逻辑器件。

CPLD开发软件用ISE 6.0+ModelSim 5.7SE,该软件是一个完全集成化、易学易用的可编程逻辑设计环境,并且广泛支持各种硬件描述语言。他还具有与结构无关性、多平台运行、丰富的设计库和模块化的工具等许多功能特点。

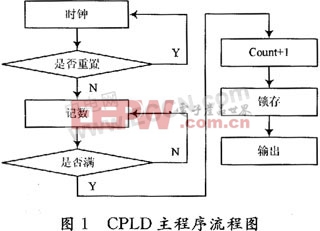

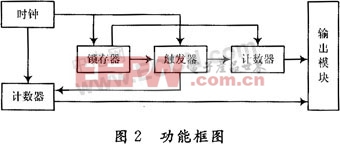

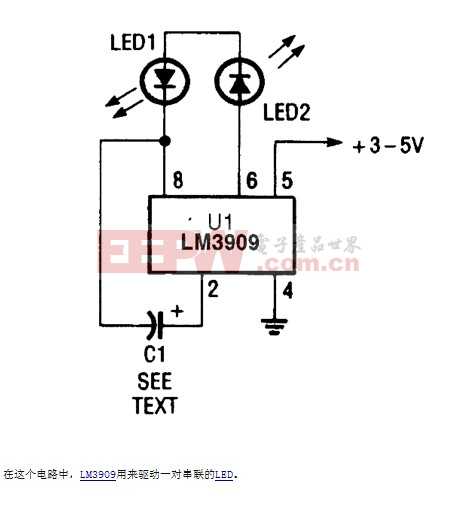

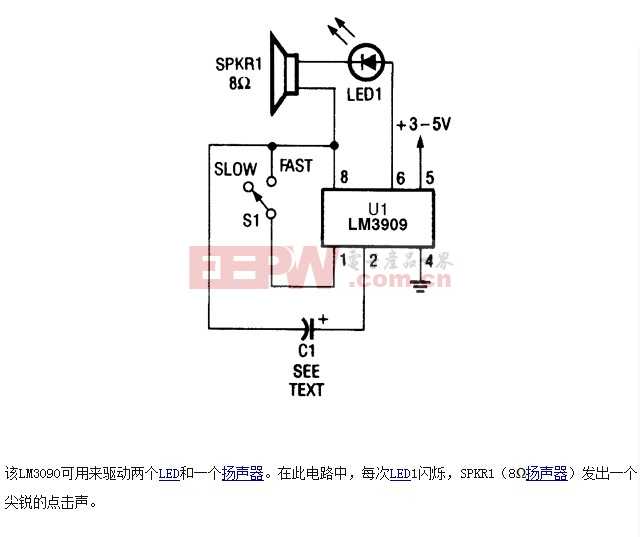

CPLD主程序流程图如图1所示,时针信号是整个程序的关键,通过时钟对各个模块进行精确控制,实现基本功能。时钟信号的精准度决定了输出脉冲信号的精准度。时钟源采用了4脚晶振,可以输出一个稳定的时钟信号。CPLD内部电路资源分配如图2所示。

|

时钟信号和复位信号作为输入信号,控制脉冲信号的输出。系统分4个模块,包括计数器、锁存器、触发器和数据输出模块。时钟信号和复位信号分别加在计数器和触发器上,计数器计数通过锁存,在时钟信号作用下同步触发输出信号。当复位信号到来时,计数器重新清零计数。

|

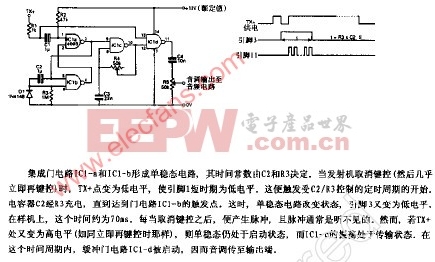

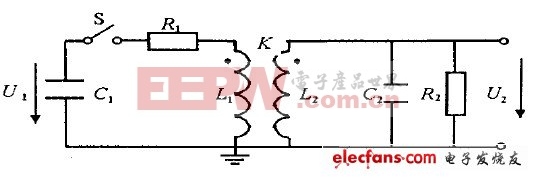

当时钟的上升沿到来时对高频时钟进行计数,CPLD内部建立一个5位计数器,计数器满后自动重置为0,输出端把计数器的各位进行输出,计数器满后也输出一个高电平。第一级输出端一共有7个,可以实现对时钟的2,4,8,16,32,64分频以及单脉冲输出。在CPLD内部再建立一个3位计数器,对前级4分频信号再做计数,调节占空比,控制脉冲输出,同时对一级分频信号进行相与输出。设置一个复位端,当高电平时候,对电路进行复位,计数器重新开始工作。通过复位端可以很好地控制脉冲输出,并且输出信号脉冲宽度在不同的分频接口可以得到不同的脉冲宽度信号,也可以通过修改程序实现脉冲宽度的改变。CPLD外围硬件电路包括了电源、晶振、输出端口、指示灯,如图3所示。

相关推荐

技术专区 |

评论