在后版图网表上优化泄漏功率

摘要

本文引用地址:https://www.eepw.com.cn/article/191223.htm随着泄漏功耗成为待机模式下的主要能耗,降低泄漏功耗也成为客户实现节能的主要途径之一。故现有的实现流程中需要采用快捷的解决方案,不仅对设计收敛影响最小,还应尽可能地缩短执行的汇聚时间。

建议的方案适合于那些采用双/三重 Vth (阈值电压) 技术、无需对现有 RTL 至 GDS 流程做任何修改的设计。

引言

泄漏功耗是固有的静态功耗,与开关及内部功耗 (定义为动态功耗) 共同构成总体功耗。

泄漏功耗与应用无关,主要是来自于:

● 源漏亚阈值 (sub-threshold) 电流,这是阈值电压降低以致沟道不完全关断的结果。

● 栅极到沟道的泄漏电流。

在多Vth技术中,亚阈值电流与Vth成指数关系,故低Vth单元的速度更快,但泄漏功耗也要大得多。

随着工艺尺度的缩小,这种情况愈加严重,而且在90nm及以下工艺节点,对大多数移动应用而言,这一问题越来越显著。

降低泄漏功耗是一项贯穿架构设计、VLSI设计、综合、PR (布局布线) 直至Signoff (完成) 的任务。

功率设计包括减少关键和次关键路径的数量,以便在可能时让更多的单元被映像到高Vth上。

智能综合 (smart Synthesis) 与PR的使用对设计的最终泄漏模式也有很大影响。

本文介绍的泄漏减少方法焦点在于流程实现的最后阶段,而且,虽然它主要是针对PrimeTime编写,却并不局限于某个专用PR/Signoff工具。

方法描述

1.全流程概述

这种泄漏功耗优化方法瞄准最后阶段的后版图设计工作。其概念是让设计利用基于多个Vth的交换策略,提前一步实现最大泄漏的优化。

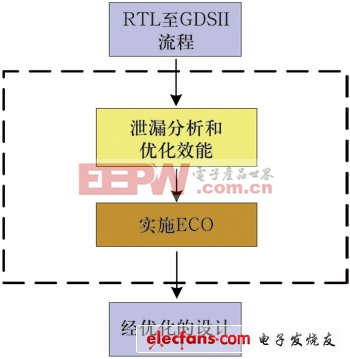

图1是整个流程的模块示意图,其中黄色和褐色矩形框代表泄漏优化。这个用于验证客户设计的系统运行在PrimeTime/StarExtract原始signoff环境下。

这种方法在完整的RTL至GDSII流程之后让最终设计进入原始signoff环境,然后开始搜索那些能够被交换到相应的更高Vth而又不会影响设计性能的单元。

基本上,这意味着这种优化将在设计的正Slack (时间裕量) 路径上进行。

在优化过程中,需检查下列设计参数:

● 建立时间违反

● 设计规则,如最大传输时间 (max_transition) 违反和最大电容 (max_capacitance) 违反

● 由衰减受害者 (victims) 引起的串扰 (Crosstalk) 违反

● 时钟网络 (Clock nets) 设计规则

● 不应被接触或改变的特殊单元和结构

● 不同模式和边角 (比如功能性/测试模式WC/BC 等)

泄漏减少流程的第一个阶段 (即示意图中的黄色矩形框) 是优化流程中主要的耗时部分,并涉及利用PrimeTime“what-if”分析的搜索和交换策略。这一步骤会反复进行,直到找到所有适合交换的单元。

优化流程的第二阶段 (即示意图中的褐色矩形框) 是后版图设计 (ECO) 上的交换执行,RC提取 (RC-Extraction) 和整个STA 运行,并重新运行全部signoff 环境。

优化流程在这一阶段对“what-if”分析与全部RC提取之比较后发现的违反错误进行修正。与PrimeTime的快速计算以及总体运行时间减小的的优点相比,这些错误就相对不起眼了。因此,这一步骤的反复次数应该较小。该阶段的缺点是需要重新运行完整提取,从而增加总体运行时间。

在所有违反都得到修正 (第二阶段) 之后,优化设计的输出在功能性上与原始的设计版图相同,但大大减少了不必要的低/标准Vth单元,因此降低了功耗。

这种方法节省的总体功耗取决于RTL编码以及RTL-to-GDS实现流程早期阶段的泄漏意识。不过,利用这种流程可确保设计在Signoff要求方面得到最大限度的优化。这个问题十分重要,因为实际实现和Signoff优化之间总是存在差距,而在优化流程之后,这一差距可被减小。

2.交换算法

这种方法的目的是尽可能找出非时序关键路径 (即正Slack路径) 上的低/标准Vth单元,并用高Vth单元来替代,同时不影响时序或任何其它设计要求。

评论