基于ADMS平台的加速混合信号集成电路设计

本文引用地址:https://www.eepw.com.cn/article/190687.htm

3. Mach

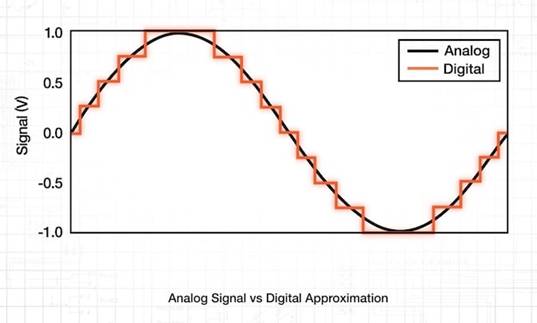

SPICE仿真的特点是精度高、速度慢。做模拟电路设计时,用SPICE仿真一般可以满足要求。但是当电路规模增加、尤其是增加了晶体管级描述的数字电路部分之后,SPICE显得过慢。相同的仿真条件下,SPICE的仿真时间随着晶体管的增加甚至不是线性上升,而是呈指数次方上升。这样电路仿真成为设计的瓶颈,这一点在后仿真阶段也经常遇到。

于是Mach作为Fast-SPICE应运而生。Mach在Eldo的基础上,通过查表方式的晶体管模型迅速提高了仿真速度。相比Eldo,Mach可以将仿真速度提升10~1,000倍。速度提升牺牲的是精度,不过损失的精度能够控制在3%之内。Mach的处理容量也是非常巨大的,最大可以达到2,000万个器件。于是对于一些精度要求不是非常严格的设计,当需要快速验证时,Mach成为必需,如存储器设计。

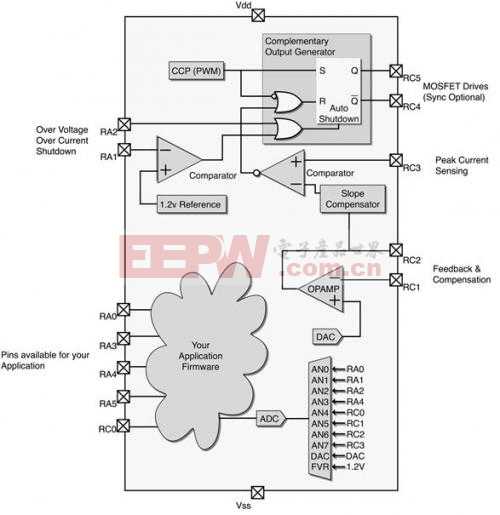

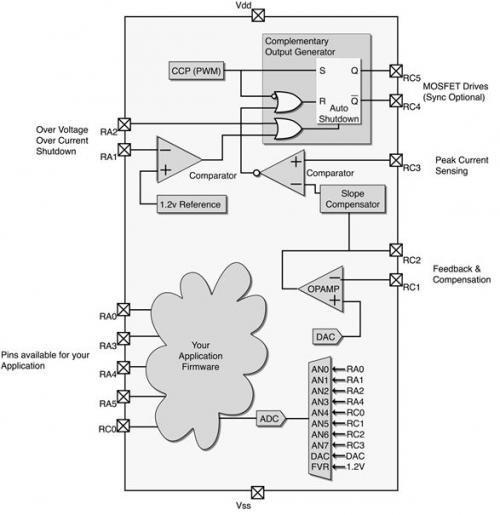

ADMS是一个混合信号验证平台,集成了以上三种工具的技术。对模拟电路部分,采用Eldo的仿真算法,或者Mach的快速仿真算法;对数字部分,采用ModelSim的仿真算法。但是ADMS并不是这些工具简单拼起来,它有单一的内核引擎。

采用ADMS进行设计,传统的数字设计流程和模拟设计流程被打散并重新组合,设计师可以在任何阶段对电路进行验证,数字设计和模拟设计通过ADMS组成一个整体。

最新发布的ADMS4.0版增加了SystemVerilog语言和SystemC支持,这使得ADMS支持的语言达到了八种,即VHDL、Verilog、SPICE、VHDL-AMS、Verilog-AMS、SystemVerilog、SystemC 以及C,涵盖了目前大部分的集成电路设计语言。这使得用ADMS进行设计时方法灵活多变,而工具却只有一个。输入ADMS的文件可以只有一个,不管其中的内容是HDL、SPICE,还是C语言,ADMS都可以读入,并自动进行处理,给出仿真结果,例如在模拟电路中引入一个HDL描述的IP,或者是工具附带单元库里的一个VHDL-AMS行为级描述的运放单元,各种语言可以无缝地组合到一起。

ADMS提供了灵活的使用方式。它既可以集成到Mentor Graphics的电路图编辑工具DA-IC中,也可以集成到Cadence的Schematics Composer中(图3),另外还可以单独使用。应用时ADMS的界面与经典的ModelSim相似,操作简单,其树状结构显示使得整个设计一目了然。使用时只需要读入输入的各种文本文件(可以以数字结构为最顶端层次,也可以以模拟结构为最顶端层次),即可由ADMS进行仿真和调试。

ADMS的输出文件可以被其它工具的多种波形观察工具查看和计算,不过ADMS附带有两个功能强大的波形处理工具Xelga和EZwave,可以同时处理数字和模拟信号,并进行各种操作与运算。

Eldo RF在Eldo的基础上发展而来,针对射频电路使用了新的技术,ADMS也可以扩展到ADMS RF,成为针对射频混合信号SoC设计的工具。

ADMS附带了很多行为级描述的单元库,称为CommLib,其中包括三百多种常见的基本单元,如ADC、DAC、PLL、Σ-Δ、OP等等。各种库提供了大量的接口参数供修改,在设计中可以直接调用这些单元库,增加仿真速度,以及方便调试电路。CommLib还有一个“行为级模型校正”(BMC,Behavior Model Calibration)的功能,通过BMC以及ADMS的验证,可以将所设计的电路图抽象到行为级。在仿真的时候,行为级的仿真速度比晶体管级快1,000倍,这样可以将部分电路抽象到行为级,从而增加仿真速度,并方便调试。抽象化技术在大规模电路设计中越来越得到频繁应用。

本文小结

ADMS是一种真正意义上的模拟/混合仿真工具,它可提供全面的语言与设计方法支持。目前,中国真正在做混合信号设计的设计师虽然不多,但毫无疑问,正在逐渐增加。那么,究竟在什么样的情况下,需要转到混合信号设计呢?也许可以简单地作这样一个描述:当使用HDL仿真器的数字电路设计工程师面临增长的模拟部分和模拟电路行为,却苦于不足的模型以及仿真精度时;当使用SPICE或者FastSPICE的模拟电路设计工程师,面临增长的数字复杂度以及大规模,苦于仿真速度过慢时。这些时候,采用混合信号设计,就可以提升设计速度和效率以及设计水平,并降低产品成本。

评论