ISP型PLD的图像处理系统硬件设计

2.2 图像采集时序的产生

这里,以256×128点阵为例,说明图像采集时序的产生。

以A0~A7表示每行中点阵的地址,A8~A14表示行地址。其行有效信号和A0~A7地址的时序如图2所示,其场有效信号和A8~A14地址的时序如图3所示。这样共用256×128=32

768个存储单元存储1幅图像。

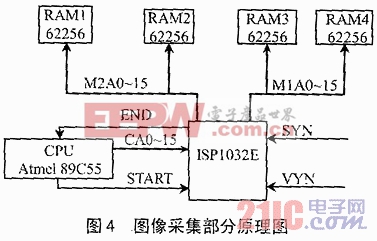

如果需要采集图像,由由CPU给ISP发出START信号,令ISP断开CPU提供给图像RAM的地址线,改由ISP产生图像RAM的地址A0~A14。SIP产生完1幅图像的地址后,输出1个END信号,通知CPU采图完毕,并让出RAM的地址线和数据线给CPU,供其进行图像处理。

系统中共有4片32K×8bit的RAM(62256),其中:

RAM1为图像帧存;

RAM2为图形标志位,用于图像的标注;

RAM3为菜单界面的显存;

RAM4为系统内存,用来存储处理的中间数据和处理结果。

图4为图像采集部分原理图。

在实际使用中,CPU对RAM1、RAM4与RAM2、RAM3的操作是分时进行的。在扫描期,CPU对RAM1和RAM4进行操作,进行图像的计算和结果处理;而在回扫期,则进行菜单和标注的刷新。ISP对RAM2和RAM3的操作是在扫描期,

进行菜单和标注与图像的合成输出。

ISPEXPERT的LATTICE公司于20世纪90年代末推出的一套完整的ISP集成开发环境。它

有500个宏元件可供调用,支持VHDL、Verilog-HDL、ABELHDL和原理图编译器一体的开发软件;可用于ISP器件的逻辑设计和优化、逻辑映射、自动布局布线、生成熔丝图文件和编程下载。此外,它还可以对设计的数字系统进行功能仿真、时序仿真和静态时序分析。

从使用者的角度看,ISPEXPERT比Workview

office和Synario软件功能更强大,操作更方便。

本系统采用ISP1032E芯片省略了复杂的、大量的逻辑电路,利用VHDL语言编程,通过ISPEXPERT集成开发环境开发,既节省了大量的硬件调试时间,又减少了线路间的相互干扰。更重要的是节省了重复制板的时间,大大缩短了产品开发周期。

结束语

基于ISP和单片机构成的图像处理系统,具有结构简单、集成度高、体积小、价格低廉等特点,尤其适用于具有图像处理功能的嵌入式系统的开发。本系统已在实际中使用,取得了良好的效果。

超级电容器相关文章:超级电容器原理

评论