用CPLD实现FIR数字滤波器的设计

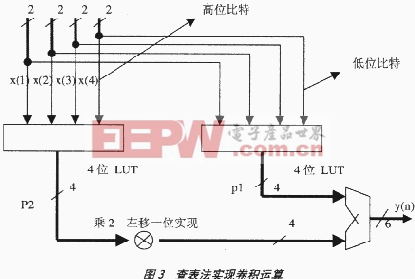

和“011”是由不同的h(n)之和构成,而对h(n)的选择是由乘数x(n)的相同位的比特决定的。例如上图x(n)的最低位为1001,则p1的值为h(1) + h(4);其高位为1010,则p1的值为 h (1) + h(3)。因此利用Altera公司FLEX器件中的查找表(LUT)结构,预先将h(n)的各种组合存入查找表,则上例中的原需4次乘法 和3次加法的卷积运算转化为1次加法。图3显示了用查找表实现该例的结构。

和“011”是由不同的h(n)之和构成,而对h(n)的选择是由乘数x(n)的相同位的比特决定的。例如上图x(n)的最低位为1001,则p1的值为h(1) + h(4);其高位为1010,则p1的值为 h (1) + h(3)。因此利用Altera公司FLEX器件中的查找表(LUT)结构,预先将h(n)的各种组合存入查找表,则上例中的原需4次乘法 和3次加法的卷积运算转化为1次加法。图3显示了用查找表实现该例的结构。 用查表法实现卷积运算时,有并行和串行两种结构。图3中为并行结构,其中两个LUT是完全相同的。在并行结构中,LUT的数量根据x(n)的数据宽度决定。一位对应一个LUT,这样速度达到最大,在FLEX10K的结构中提供了两条专用数据通道,即进位链和级联链,通过级联链相邻的LUT可以用来并行计算函数的各个部分。

利用FLEX10K芯片实现FIR数字滤波器

FELEX10K系列芯片具有查找表结构,利用其实现采用全局并行的FIR数字滤波器,也即将输入x(n) 经过不同的延迟后同时进行处理。

FELEX10K系列芯片具有查找表结构,利用其实现采用全局并行的FIR数字滤波器,也即将输入x(n) 经过不同的延迟后同时进行处理。FIR数字滤波器的层次结构图如图4所示:

本文引用地址:https://www.eepw.com.cn/article/188815.htm

控制器模块(contr)的作用是产生控制信号对延迟、并串转换、抽头系数、移位相加模块进行控制,以使它们按一定的形式组合在一起实现滤波器功能。控制器模块在接收到A/D转换结束信号后,依次产生移位寄存器使能信号、并行到串行转换的装入信号、移位相加的装入信号、加减控制信号和滤波结果输出信号等各种控制信号,使上述各个模块按照一定的时序进行操作,从而完成滤波功能。时延环节模块(shift-reg)的作用为使A/D转换后的数据通过不同的触发器,进而产生不同的延迟。并/串转换模块(p-s-ff)的作用是将通过时延模块产生的不同延迟分别同时转换为查找表的串行地址,提供给抽头系数模块。抽头系数模块(sub-rom)将抽头系数的各种组合固化在ROM中。它的地址输入端接收并/串转换模块的串行输出,然后查表得到卷积的中间数据.。移位相加模块通过将中间数据移位相加而实现两个数相乘的功能。

评论