一种高速低压用增益增强型运算跨导放大器设计

按照12位100MHz采样频率流水线A/D转换器的采样保持电路的指标来设计这个运算放大器。对动态误差和静态误差所各自需要的增益和单位增益带宽进行了折衷,将0.002%分配给静态误差,余下的0.008%给动态误差。电路采用中芯国际(SMIC)0.18 μm混合信号CMOS工艺设计,1.8V电压供电。具体设计指标为:开环增益:102dB:建立时间:4.3ns;精度:0.01%;单位增益带宽:1.27GHz。频率响应的曲线如图4所示。本文引用地址:https://www.eepw.com.cn/article/188745.htm

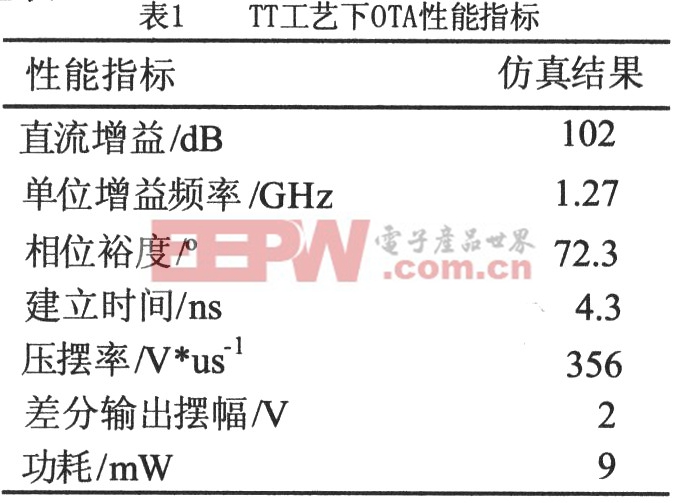

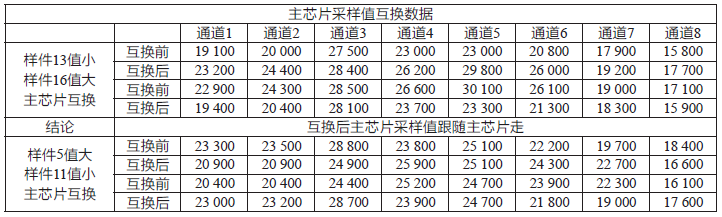

对运算放大器一些重要的性能参数在TT下仿真,结果的归纳见表1。

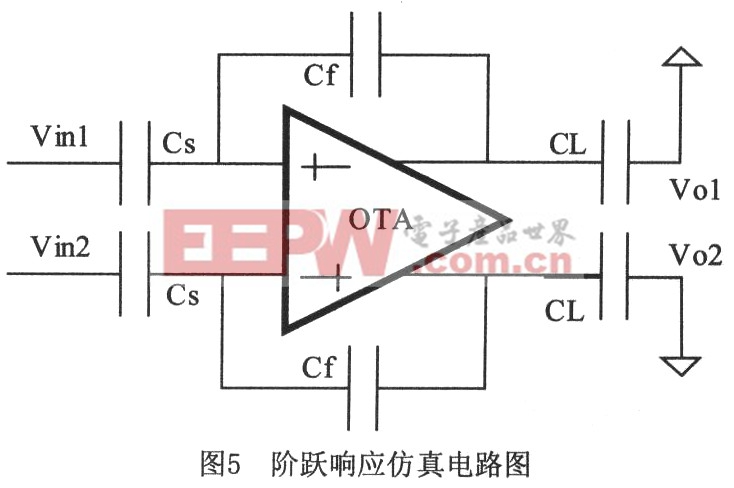

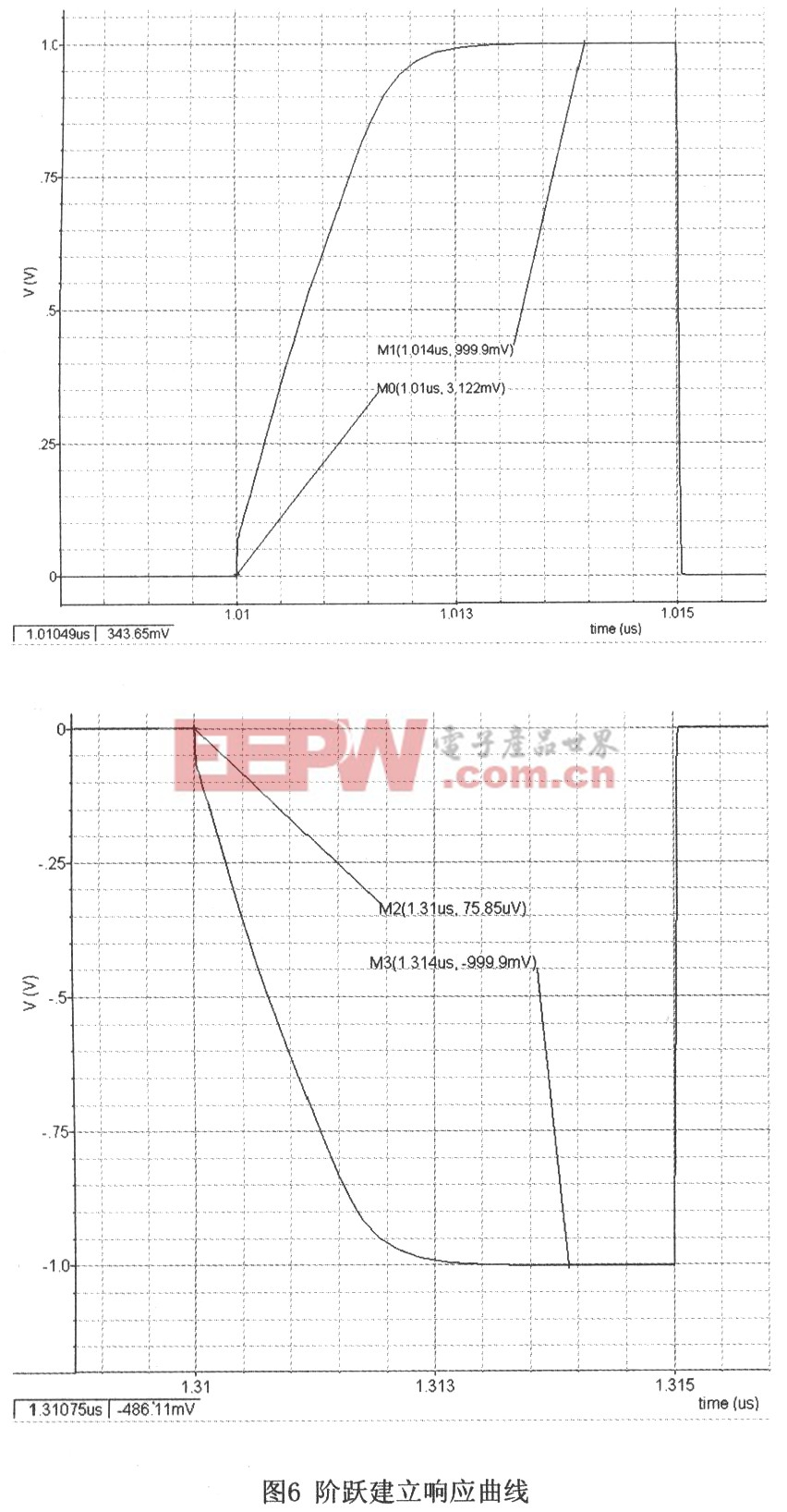

对阶跃输入响应的仿真在如图5所示的闭环中进行。从运算放大器的输入端引入一个±1V的大阶跃信号,对应的建立时间曲线如图6所示,表明所设计的电路能够在4.3ns内达到终态0.01%的精度。

3 结论

本文提出了一种可用于增益增强运放高速设计的优化方法,并采用SMIC 0.18 μm混合信号CMOS工艺设计,实现了一个单级全差分增益增强的折叠共源共栅运算放大器。详细分析并克服了零极点对可能引起的慢动态性能。仿真结果表明,此运算放大器能够满足高性能流水线A/D转换器设计的要求。

评论